01

PCIe 7.0 带来的插损挑战

SUNSHINE GLOBAL CIRCUITS

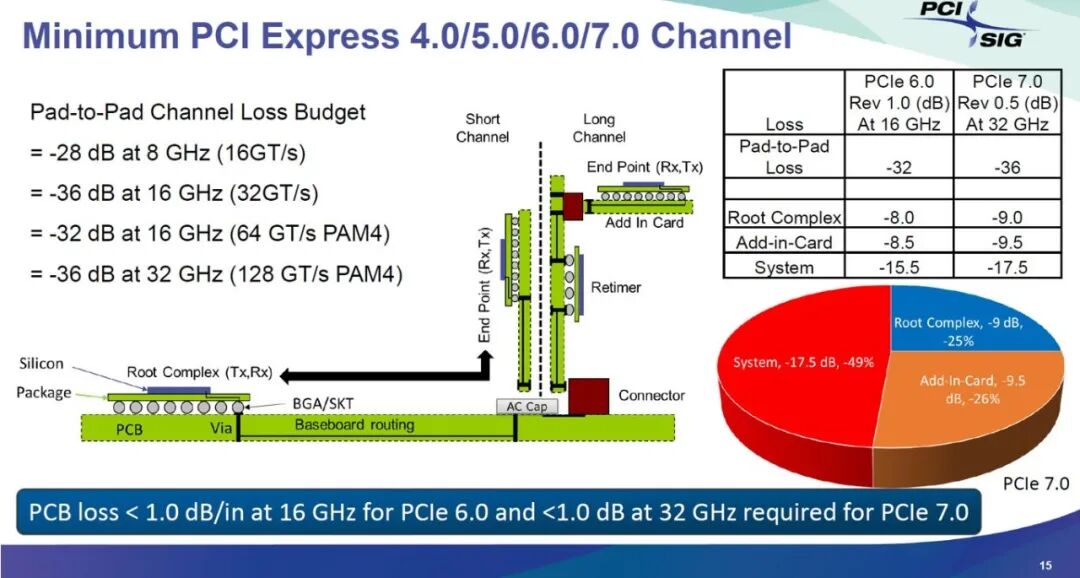

随着AI算力需求爆发,服务器数据总线带宽要求急剧攀升。以PCIe为例,其协议已演进至PCIe 6.0/7.0,信号速率达64GT/s并迈向128GT/s,通道配置扩至x16,通过提升频率与并行度来实现超大带宽通信。

与此同时,信号频率的飙升导致PCB插入损耗呈指数增长,引发信号衰减与失真。PCB走线阻抗的不连续性会带来反射与时序抖动,共同造成信号完整性的问题。

PCIe规范演进

PCIe 7.0为实现高达128GT/s的超高速数据传输,以及由此带来的严苛插入损耗和阻抗设计挑战,采取了多项协同措施。

核心在于延续PAM4调制并结合先进的FEC技术,显著提升信号的鲁棒性和抗干扰能力。此外,引入自适应均衡器动态补偿传输链路的频率响应失真,有效抵消插损的影响。

物理层设计方面,采用低损耗高速PCB材料,并将阻抗公差控制在±3到±5%以内,以减少信号衰减。

在封装与接口层面,通过改进连接器设计缩短信号路径、降低串扰,从而减少信号反射和损耗。

02

什么是插入损耗?

SUNSHINE GLOBAL CIRCUITS

PCB中的插入损耗是指信号在通过PCB传输线(如走线、过孔等)时,信号强度(功率)的衰减量,通常以分贝(dB) 计量。

PCIe 7.0 对信号链路损耗的要求

插入损耗本质上衡量的是信号在传播过程中能量的损失,是高速通信系统中衡量信号完整性的关键指标,主要由以下几类损耗构成:

导体损耗(Conductor Loss)

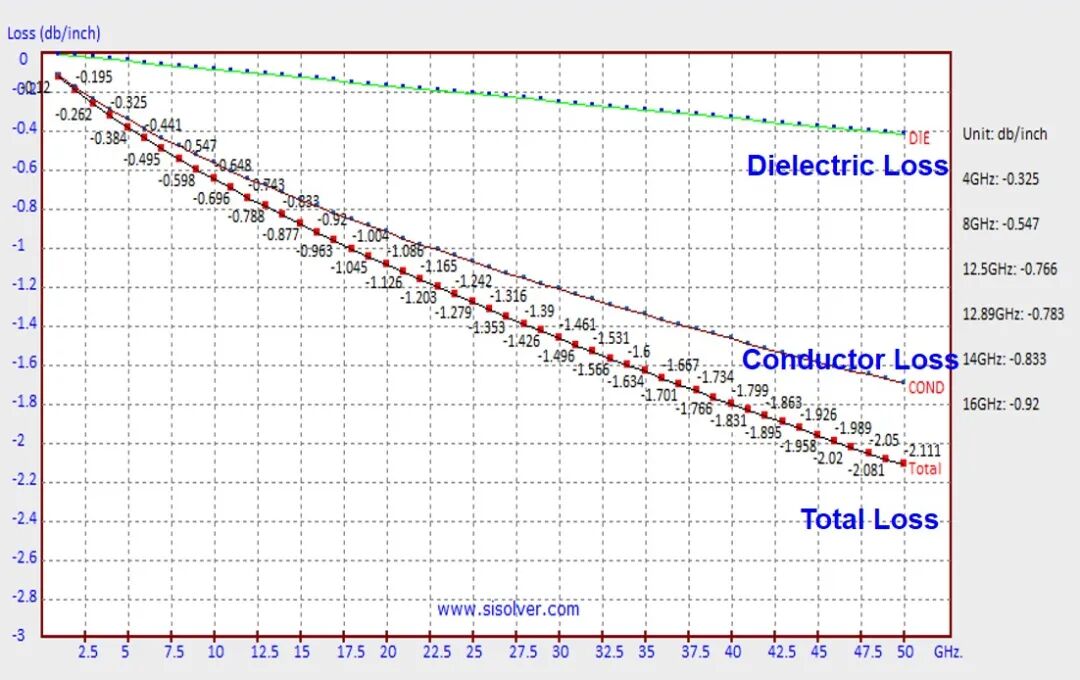

在高频和高速PCB板上,导体损耗往往占据主导地位。

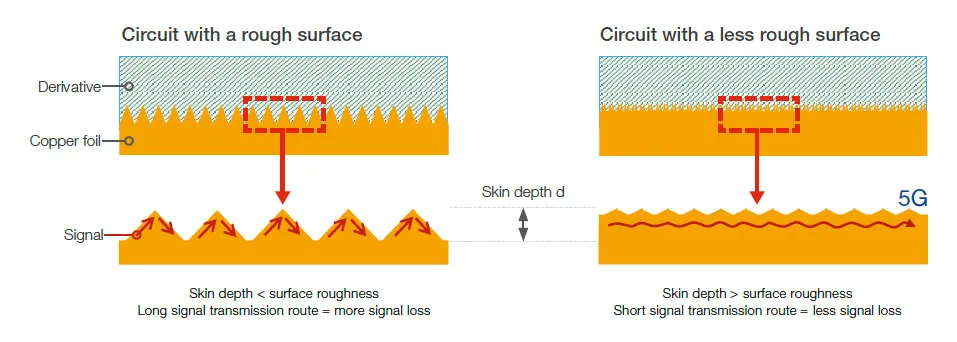

当信号的频率提高时,高频电流倾向于在导体表面流动,导致有效导电截面积减小,电阻增加。频率越高,趋肤深度越浅,损耗越大。

粗糙的铜表面会迫使电流路径变长、变曲折,并产生寄生电感,显著增加高频下的电阻和损耗。使用更光滑的铜箔(如HVLP)可以降低该损耗。

铜面粗糙度对信号传输的影响

导体损耗,高频下受趋肤效应和铜表面粗糙度影响显著,导致信号能量以热能形式耗散。

介质损耗(DielectricLoss)

信号在PCB板(介质材料)中传播时,介质材料中的分子或偶极子会试图跟随电场方向变化而发生极化和弛豫,造成部分电能转化为热能,这部分损耗称为介质损耗。简单来说,信号的部分能量被PCB基板吸收走了。

介质损耗取决于基板材料的损耗因子(Dissipation Factor, Df,也称损耗角正切 tanδ)。Df 值越高,介质损耗越大。

损耗大小与频率成正比,频率越高,介质损耗越大。

选择Dk(介电常数)和Df(损耗因子)更低的“低损耗”高速材料是降低介质损耗的关键。

不同频率下的导体损耗与介质损耗

辐射损耗(Radiation Loss)

信号能量以电磁波的形式从传输线结构中辐射到周围环境中而导致的损失。传输线在某种程度上相当于一个低效的天线。

频率越高,越容易辐射,损耗越大。

微带线(信号走在表层,有裸露的场)比带状线(信号埋在两层地平面之间)更容易产生辐射损耗。

较厚的基板和较低的介电常数会增加辐射损耗。

在阻抗不连续点(如连接器、过孔)和信号发射区域尤为明显。

03

插损的测试 Delta-L(Delta-Loss)

SUNSHINE GLOBAL CIRCUITS

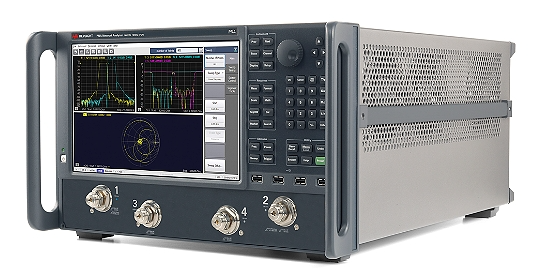

矢量网络分析仪(VNA)是测量插入损耗最便捷的仪表,它的每个端口内部包含有信号源和接收机,我们可以通过端口1的信号源发出信号给被测件,再由端口2的接收机测量经由被测件处理后的输出信号,矢量网络分析仪可以直接比较和显示输出信号和输入信号的差异,即为直接测量S21参数(正向传输系数),从而直观的反映信号从输入到输出的损耗。

Keysight PNA-N5224B(43.5GHZ)

明阳电路使用的矢量网络分析仪

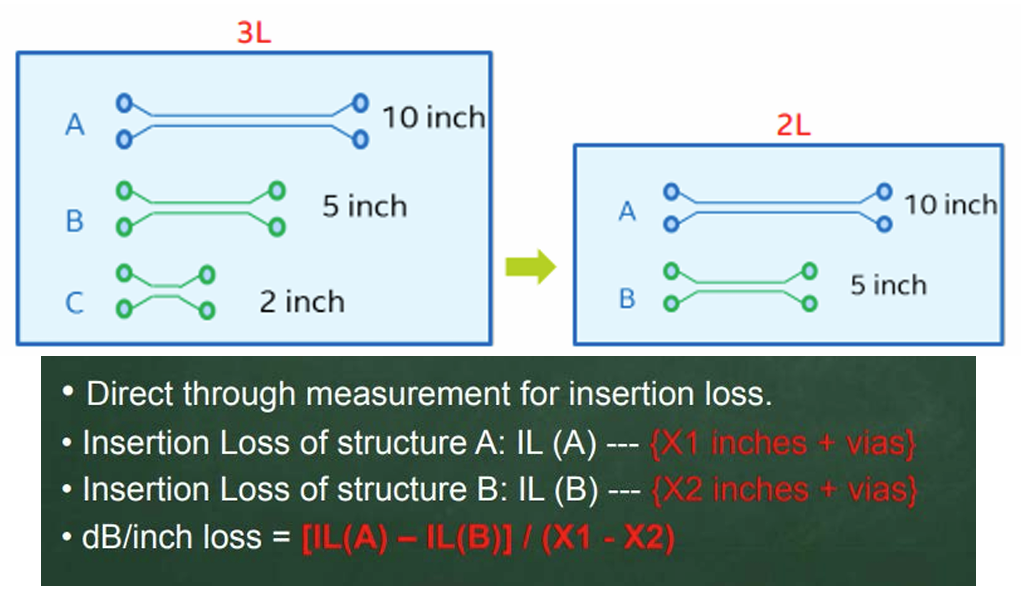

Delta-L方法是Intel开发的,通过设计两条不同长度的传输线,测试它们的S参数后进行拟合运算和差值,从而得到单位长度的插入损耗。

相比直接除法,Delta L在计算差值时数学上移除测试夹具、探针、过孔等引线(Lead-in/Lead-out)的影响,从而计算出目标PCB层上纯走线段的每英寸插入损耗。尤其在高速、高频场景下显著提升了精度和稳定性,已经成为当前PCB量产测试的主流方法。

Delta-L 插损测试方法

VIP复盘网

VIP复盘网