OpenAI的最新研究提出了利用这些嵌入式逻辑桥在更远距离之间进行高速互连的想法,使更多的芯片能够连接在一起。

OpenAI在一项名为“通过嵌入式逻辑桥连接高带宽内存芯片、I/O 芯片和计算芯片”的新专利中,分享了一种 AI 芯片解决方案的计划,该方案将包含多个 HBM 芯片和计算芯片,所有这些芯片都使用嵌入式逻辑桥连接。

该研究提出了利用这些嵌入式逻辑桥在更远距离之间进行高速互连的想法,使更多的芯片能够连接在一起,以支持高性能计算和人工智能工作负载,这些工作负载需要访问大量内存才能高效运行。

目前的封装方案在HBM集成方面存在一定的局限性,因为HBM存储器通过底层金属导线与其他芯片组通信。现行的JEDEC标准要求将HBM存储器放置在计算芯片组旁边,但这种方法存在物理限制,因为金属导线与主芯片组PHY控制器之间的距离必须小于6毫米。

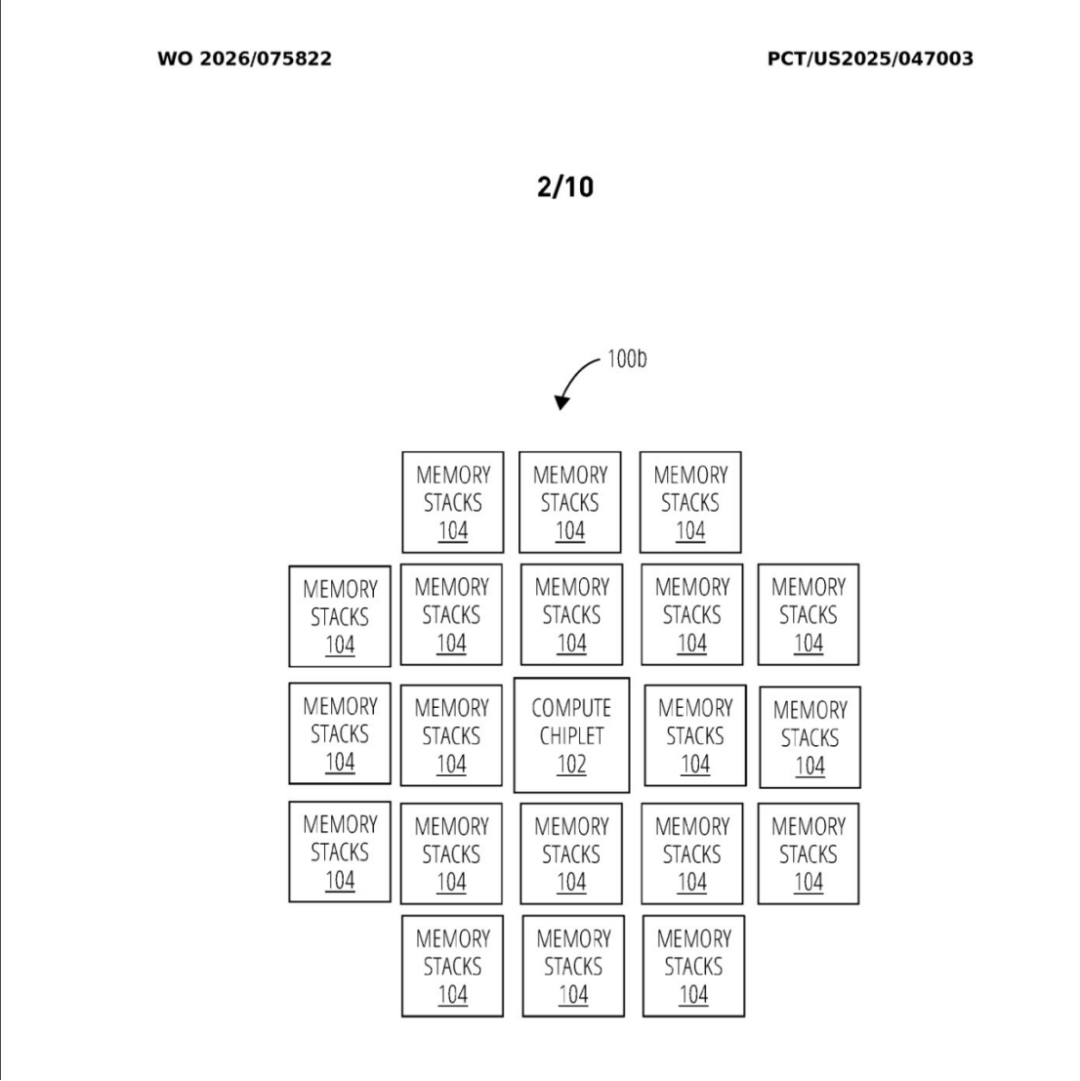

为了克服这一限制,OpenAI 的专利提出使用嵌入式逻辑桥接器,可以将通信距离从 6 毫米扩展到 16 毫米。这些桥接器具有两个优势:它们不仅可以实现更长的通信距离,还可以为 HBM 协议栈提供控制器功能,或者为封装内芯片之间的通信提供高速 PHY 功能。这种 D2D(芯片间)接口符合 UCIe(通用芯片互连高速接口)标准。

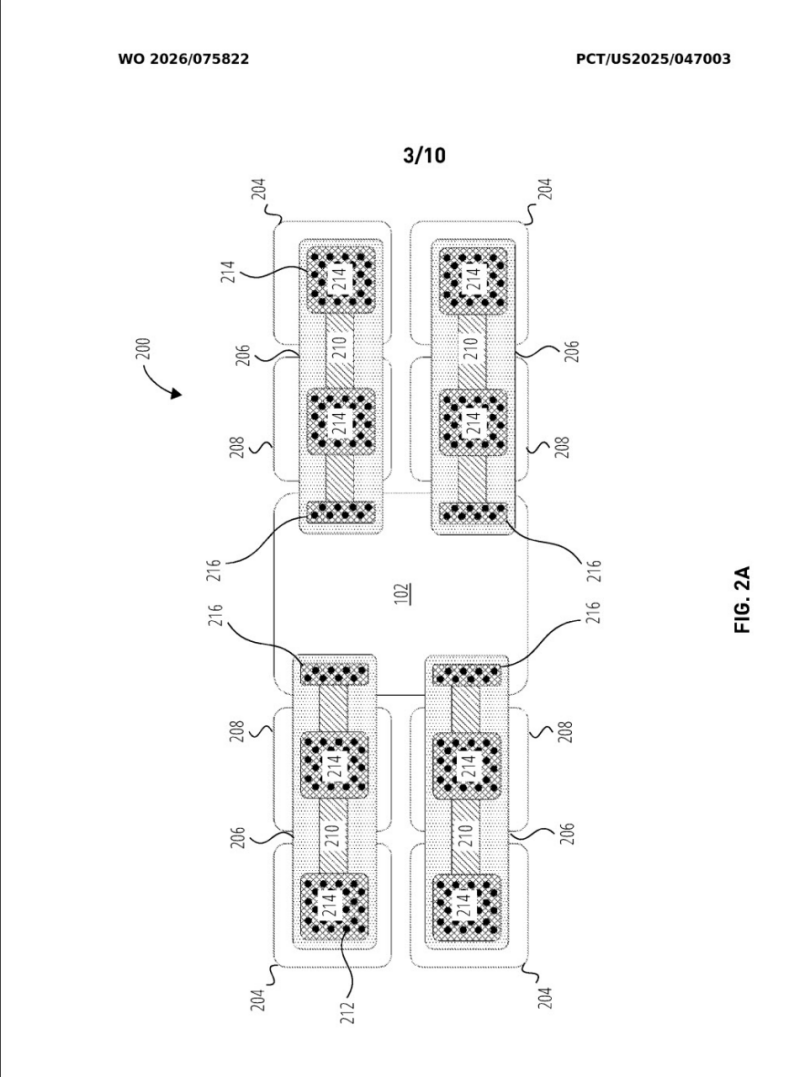

例如,OpenAI 展示了一款采用嵌入式逻辑桥接技术、拥有 20 个 HBM 内存堆栈的计算芯片。而传统方法通常只能实现 4 个、6 个或 8 个堆栈。这种技术显著提升了内存容量,使得芯片能够更好地运行大型 AI 模型。

但这项研究也与一项目前正在研发的技术密切相关。这项技术就是英特尔的EMIB(嵌入式多互连桥接)解决方案。EMIB是一种先进的封装解决方案,其作用类似于桥梁。

它旨在解决 2.5D 封装技术的问题,利用微型桥接技术扩展高性能芯片的功能和设计。EMIB 及其后续产品 EMIB-T 具有诸多优势:它们结构简单、体积小巧、突破了现有中介层的光罩限制,并且是经济高效的解决方案。

未来能否预见到,英特尔的EMIB技术会被OpenAI用于打造其定制化的AI芯片,这些芯片将包含众多芯片组和大量的HBM内存?这项专利似乎正指向这一方向。

据悉,目前英特尔一直在与至少两个先进封装服务的大客户进行持续谈判:谷歌和亚马逊,这两家公司都制造自己的定制芯片,但将部分制造流程外包。这些交易对困境中的芯片制造商英特尔来说将是一个福音,该公司正在尝试复出——部分由美国政府资助——此前经历了多年停滞并错失了移动芯片机会。

英特尔先进封装业务的野心很大程度上取决于公司能否获得这些科技巨头等外部客户。自2024年以来,公司实际上被分为两部分:长期存在的"产品"端,英特尔在此设计并向PC制造商和数据中心销售高性价比CPU;以及雄心勃勃的代工端,英特尔在此制造先进半导体。

根据2025年接管英特尔代工业务的钱德拉塞卡兰的说法,"先进封装"这个术语在十年前还不存在。

芯片一直需要某种形式的晶体管和电容器集成,用于控制和存储能量。长期以来,半导体行业专注于小型化,即缩小芯片组件的尺寸。随着世界在2010年代开始对计算机提出更多要求,芯片开始变得更加密集,包含处理单元、高带宽内存和所有必要的连接部件。最终,芯片制造商开始采用系统级封装或堆叠封装方法,将多个组件叠放在一起,以在相同表面空间内获得更多功率和内存。比如,台积电的CoWoS 严格来说便属于2.5D先进封装技术,由 CoW 和 oS 组合而来:先将芯片通过 Chip on Wafer(CoW)的封装制程连接至硅晶圆,再把 CoW 芯片与基板(Substrate)连接,整合成 CoWoS。英特尔在2.5D上有多个方案:EMIB 2.5D、Foveros-S 2.5D、Foveros-B 2.5D。当前,HBM4是使用2.5D封装的典型代表,诸如AMD、英伟达等企业已推出多款基于 2.5D 硅中介层的产品

VIP复盘网

VIP复盘网