CPO作为光模块的下一代技术,随着AI服务器互联对数据传输效率的要求越来越高,产业趋势正进一步被加强,全球头部厂商均积极探索相关技术路径和应用。我们建议关注布局CPO封装、检测等关键设备的公司。

CPO是光互联的下一代互联架构。目前,机柜间数据传输主要采用光模块进行光电转换信号传输,机柜内数据传输主要采用铜缆进行信号传输,但随着传输效率要求的进一步提高,电信号传输面临信号完整性和功耗的双重制约,因此需要引入新的互联架构以实现更高效的连接。CPO(共封装光学)通过将光学引擎与交换芯片、XPU直接集成在同一载板或者中介层上,将电信号传输路径从几厘米缩短到毫米级,从而显著降低信号衰减、功耗和延迟,有望随着技术的成熟,逐步取代可插拔光模块成为光通信的下一代技术。

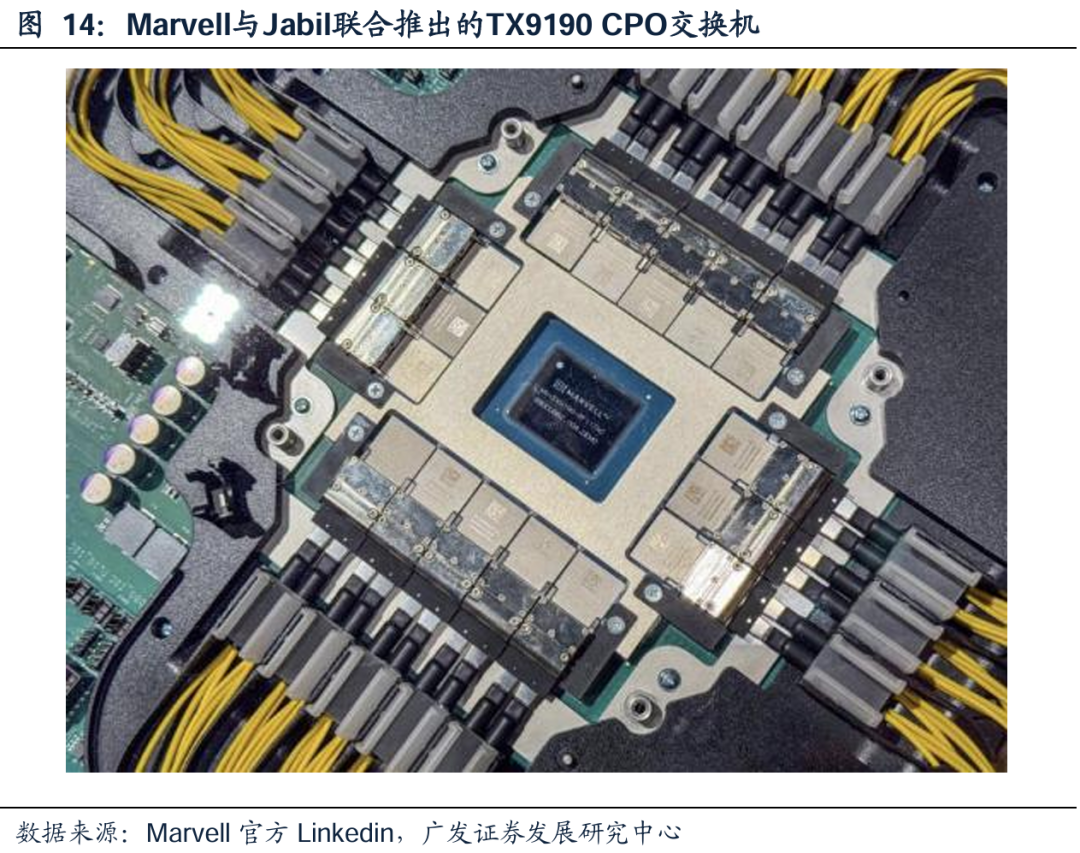

海外多家头部厂商积极投入CPO研发,商业化渐行渐近。尽管CPO技术目前仍处于商业化早期,但海外头部厂商已在CPO交换机赛道开辟专有解决方案。根据Semi analysis,英伟达推出了以Spectrum-X和Quantum-X两个系列为核心的CPO交换机,适配不同客户需求;博通CPO交换机经过两个版本的迭代已计划推出Davisson系列;Marvell也已布局全栈式CPO技术体系,最新推出TX9190 CPO交换机。

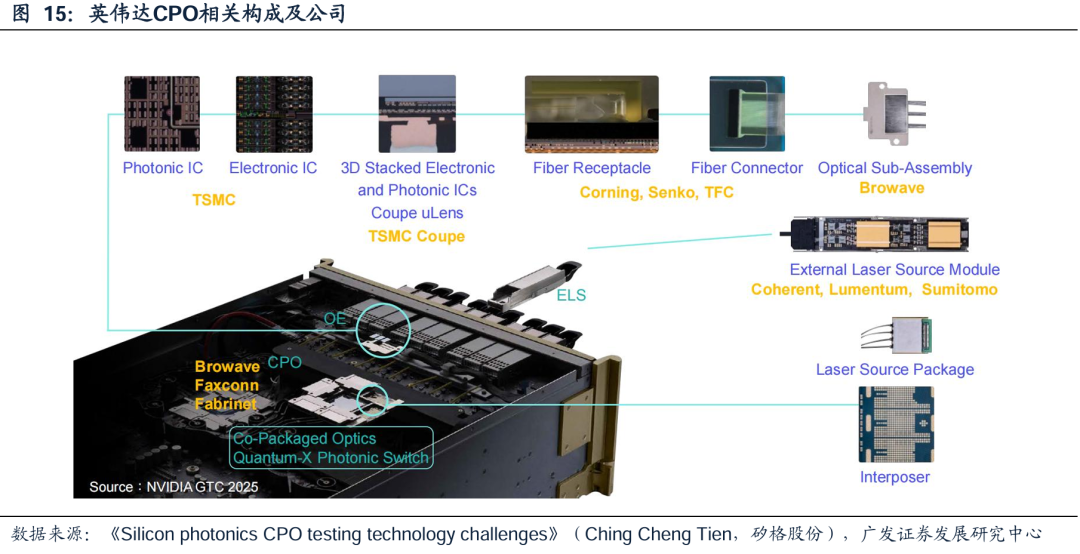

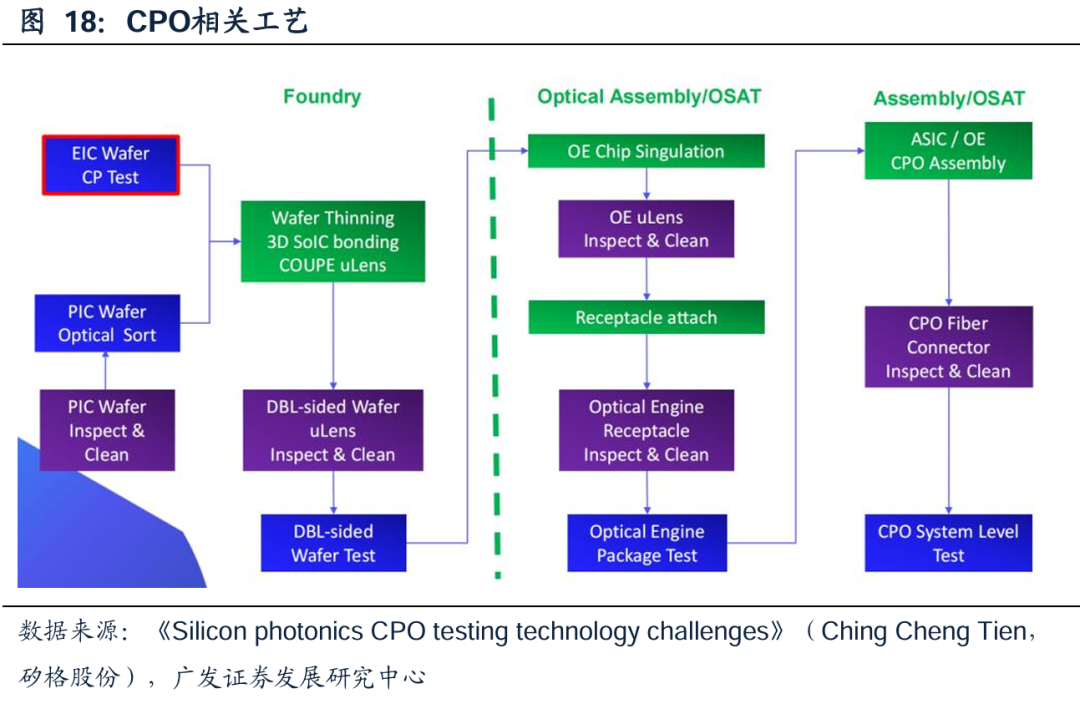

CPO制造涉及“光源 FAB 封装”等多方配合。根据《Silicon photonics CPO testing technology challenges》(Ching Cheng Tien,矽格股份),以英伟达的Quantum-X Photonic Switch为例,CPO制造涉及到的工艺/技术同时包含了前道工艺的刻蚀、薄膜沉积等以及后道工艺的键合、切片等,工序较为复杂,需要Fab端、光学组装端和封装端等多个主体共同合作。

光电测试是CPO工艺中的主要难点之一。由于CPO在制备过程中涉及了众多晶圆级加工和封装工艺,因此对CPO工艺流程的所需的光/电检测提出了更高的要求。根据ficonTEC官方Linkedin,公司在25年3月宣布推出 ficonTEC & 泰瑞达Teradyne & Femtum三方联名开发的设备,即晶圆级双面“光电”测试 激光清洁 激光修复三合一设备。

投资建议。CPO作为光模块的下一代技术,随着AI服务器互联对数据传输效率的要求越来越高,产业趋势正进一步被加强,全球头部厂商均积极探索相关技术路径和应用。我们建议关注布局CPO封装、检测等关键设备的公司。

风险提示

一、CPO:下一代光互联架构,开启高密度连接时代

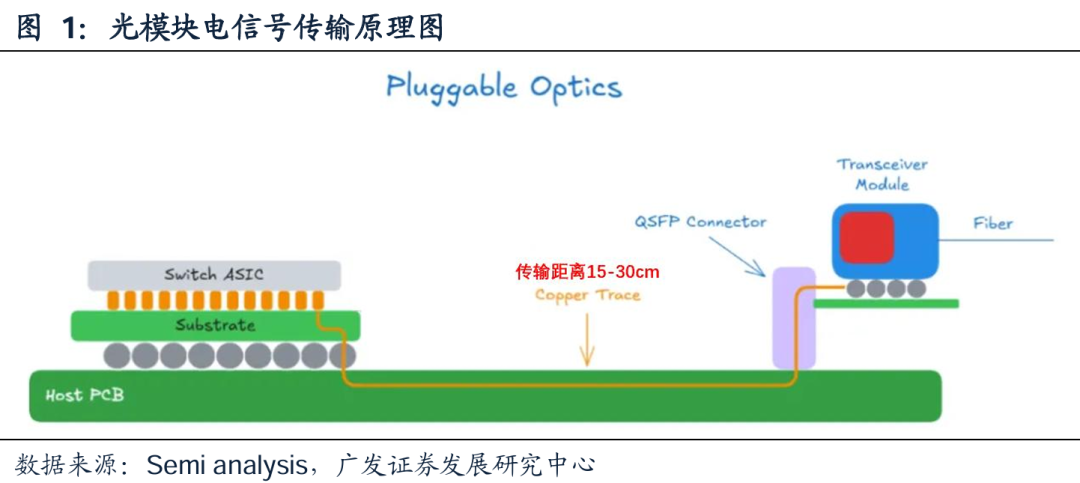

(一)CPO:传统光模块的下一技术路径,性能优势显著

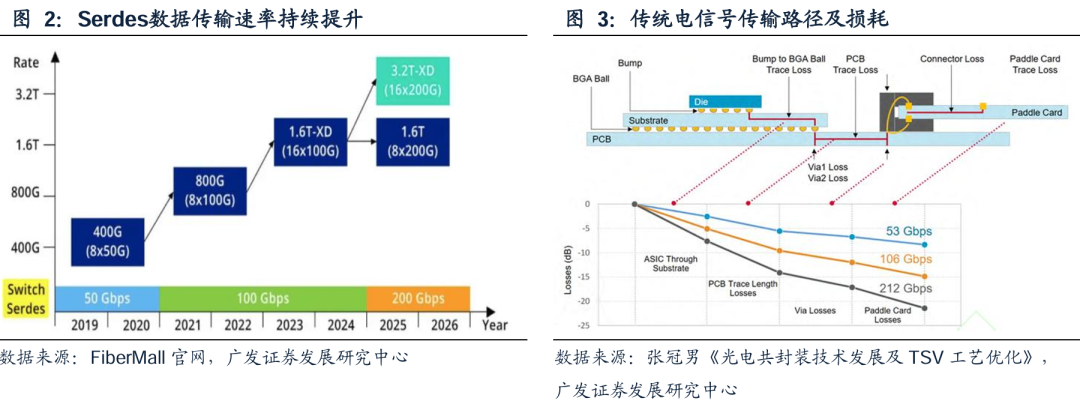

传输速率需求上升凸显传统光模块长距离电信号传输弊端。传统机柜间主要采用光模块进行光电转换信号传输,根据Semi analysis,进行光通信的光模块通常位于距离XPU或交换ASIC 15-30厘米处,因此电信号需经长距离PCB走线传输到光模块。近年来随着大模型Token消耗需求量的持续上升,数据中心的带宽和能效要求也随之提升,其中在I/O接口数量有限的情况下,SerDes的信号传输速率提升是主要方向,而这会使光模块的长距离PCB电信号传输面临信号完整性和功耗的双重制约。

电信号传输速率提升会加剧电信号长传输过程中信号失真问题。在信号完整性方面,根据张冠男《光电共封装技术发展及TSV工艺优化》,电信号在导体内的传输存在损耗,且速率越高损耗越大。在传统电芯片封装体中,1310nm波长光纤的典型传输损耗为0.35dB/Km,而高速电信号的板级传输损耗即高达5dB以上。因此,随着SerDes电信号速率的不断增大,为了满足高速信号的长距离低损耗传输,将电信号转化成光信号进行传输势在必行,其中缩短光模块核心器件与交换ASIC的电信号传输距离是主要优化方向。

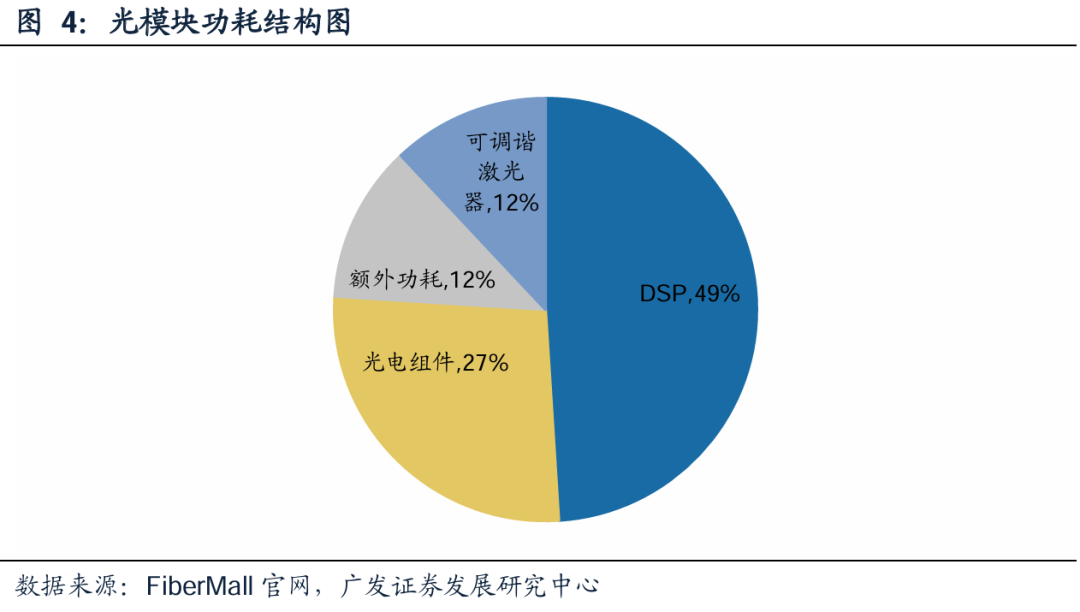

为补偿信号衰减,光模块会使用DSP芯片来重新定时和重整长距离传输来的电信号。根据Semi analysis,DSP芯片是光模块中最耗电且价格最昂贵的组件之一,在功耗层面,DSP占模块总功耗的近50%,800G和1.6T光模块中DSP芯片的功耗分别为6-7W和12-14W;在成本层面,若采用高端品牌的光模块,DSP芯片可占集群总拥有成本的近10%。因此降低交换ASIC与光模块之间的传输距离,进而舍弃DSP芯片是重要发展方向。

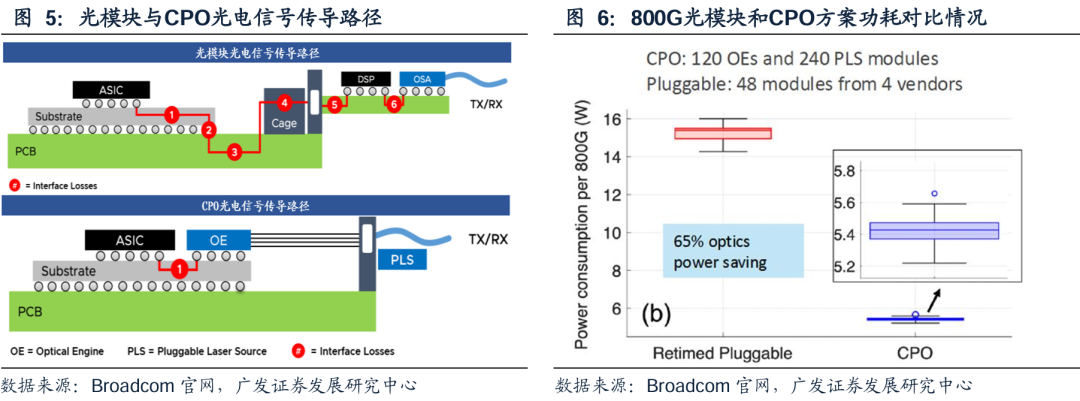

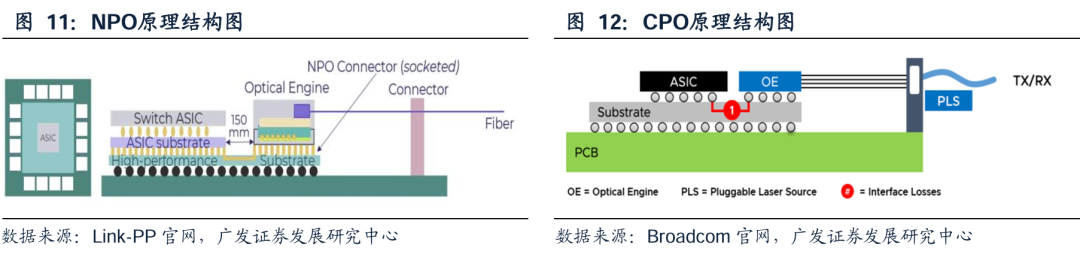

为实现短距离的电信号传输,CPO共封装光学(Co-packaged Optics)应运而生。CPO的核心理念是将光学引擎与交换芯片ASIC或计算功率芯片直接集成在同一封装中。该设计取消了传统通过前面板接口连接主板的可插拔光模块,将电信号传输路径从几厘米缩短到毫米级,从而显著降低信号衰减、功耗和延迟。根据Broadcom官网,与光模块相比,CPO核心是将原本光模块的1、2、3电信号传输步骤缩短至了只有1的传输步骤。传统800G光模块单端口功耗约为15W,CPO方案的800G光引擎单端口功耗仅为5.4W,能节省约65%功耗。

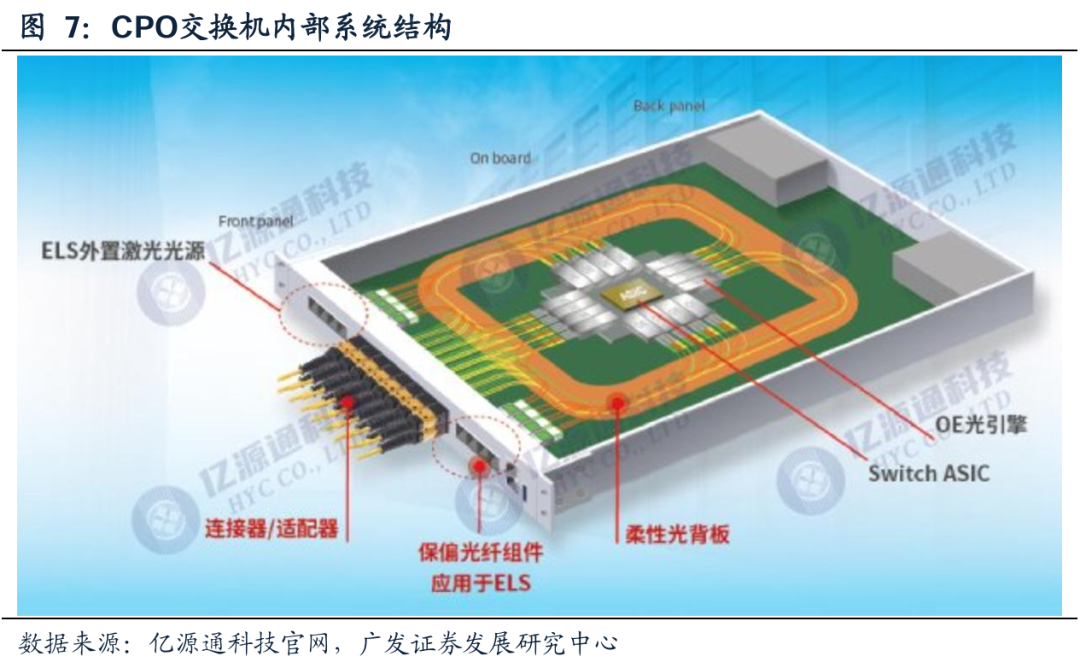

从结构来看,CPO核心变化是舍弃了DSP交换芯片并外置了ELS激光光源。根据亿源通科技官网,CPO交换机以交换芯片ASIC为中心,将OE光引擎与ASIC直接共封装在同一基板或中介层上。CPO采用了ELS外置激光光源方案,通过保偏光纤组件将纯净激光输送至光引擎内部,同时通过柔性光背板实现光信号的柔性布线与高密度连接,最终由连接器/适配器对接外部光纤链路。光引擎接收到电信号后,利用ELS注入的连续激光完成电光调制,将数据“刻”在光载波上,再通过柔性光背板和连接器输出到光纤中传输。接收端则反向操作,将光信号解调成电信号传回ASIC。

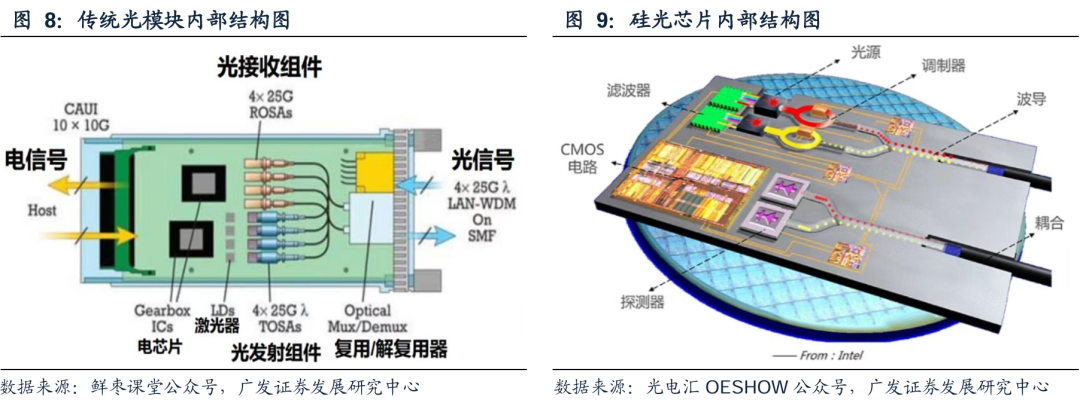

CPO与传统光模块在光引擎的核心架构上存在本质差异。CPO采用的硅光方案与传统光模块的差异核心体现在集成方式与器件构成上。传统光模块的光引擎多采用分立器件组合形式,调制器、探测器、光波导等关键光电元件相互独立,通过外部耦合、组装实现光路连接,器件离散程度高。而CPO依赖的硅光芯片则依托硅基集成平台,将调制器、无源波导、光电探测器等核心光路组件直接集成在同一芯片基底上,实现了光电器件的单片化整合,从分立组装转向芯片级集成。

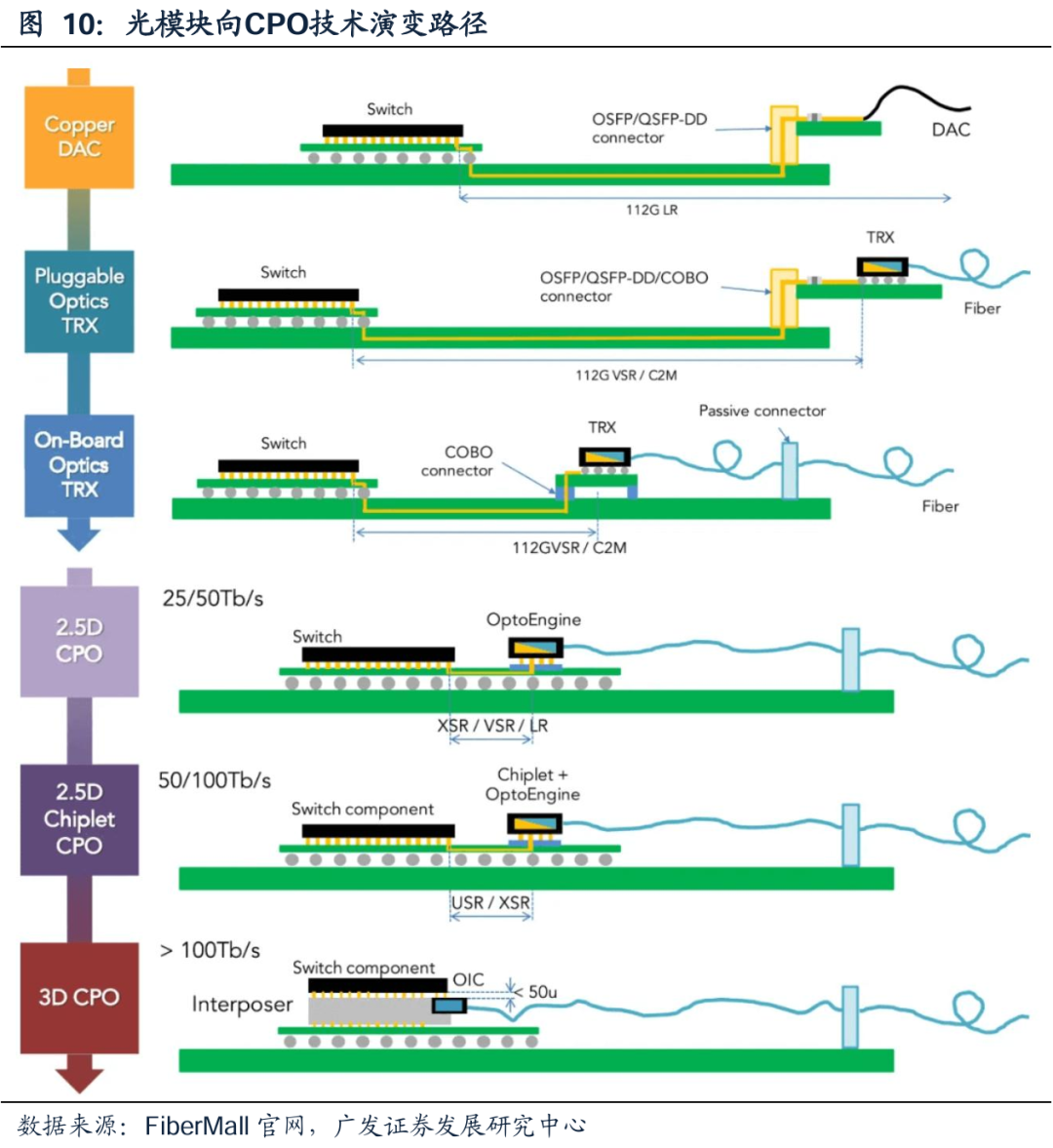

光模块向CPO的发展阶段是按照距离缩短程度和封装技术来划分。为了缩短交换芯片ASIC与光模块之间的传输距离,可插拔光模块技术先采用近封装光学NPO(On-BoardOptics)方案,在NPO中光引擎将被直接贴在芯片旁的板卡上,电互联距离大幅缩短至厘米级,有效降低了损耗与功耗,是通往CPO的关键过渡形态。CPO是从2.5D封装开始,在CPO中光引擎与交换芯片被集成在同一基板或Chiplet上,电互联距离压缩到毫米级,实现了XSR/VSR等高速电信号的低损耗传输,功耗和密度均得到革命性提升。随着封装技术向3D演进,3DCPO成为终极方向,3DCPO通过硅中介层实现芯片与光引擎的垂直堆叠,互联距离进一步压缩至50微米级。

目前NPO是光模块向CPO发展的过渡阶段,CPO与NPO的本质区别是光引擎与ASIC是否共用基板。在NPO中,光引擎与交换芯片ASIC分别封装,但安装在同一块PCB板上并通过PCB走线连接,电气互连距离较长。在CPO中,光引擎与交换芯片直接集成在同一个封装基板或封装壳体内,电气互连距离短。

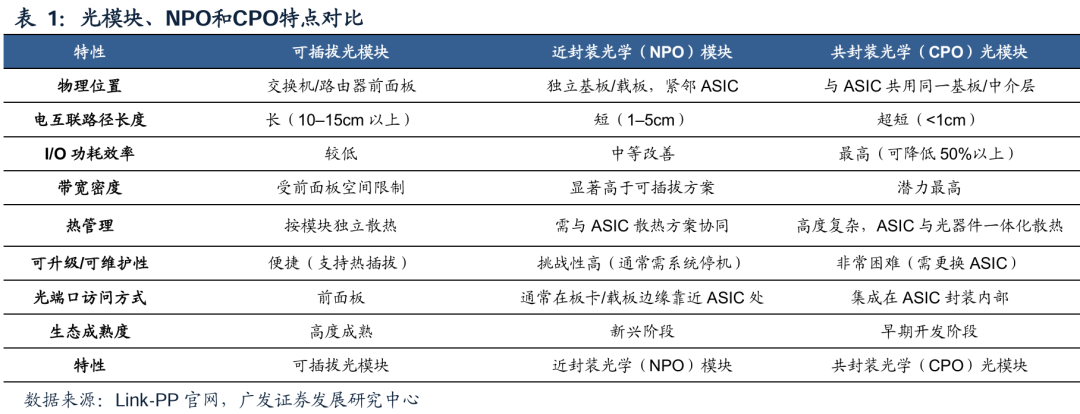

可插拔光模块虽具备热插拔、易维护的灵活性,但难以支撑800G以上速率的长期发展;NPO作为向CPO过渡的中间形态,将光模块移至紧邻ASIC的独立基板,把电互联距离缩短至1–5厘米,在功耗效率和带宽密度上实现了中度改善,能适配早期AI高密度聚合场景,但仍需与ASIC散热协同。而CPO则将光引擎与ASIC集成在同一基底/中介层,电互联距离压缩至1厘米以内,不仅能实现50%以上的功耗降低,还拥有最高的带宽密度潜力,是面向超高密度、功耗敏感型AI/ML场景的终极方案。

(二)CPO交换机:主流厂商进展迅速,即将商业化落地

CPO交换机即将商业化落地。现阶段尽管CPO技术仍处于早期商业化阶段,但主要厂商已在CPO交换机赛道开辟专有解决方案。英伟达CPO交换机以Spectrum-X和Quantum-X两个系列为核心,博通CPO交换机经过两个版本的迭代已计划推出Davisson系列,Marvell也已布局全栈式CPO技术体系,最新推出TX9190 CPO交换机。

1. 英伟达:发布两款CPO交换机Spectrum-X和Quantum-X

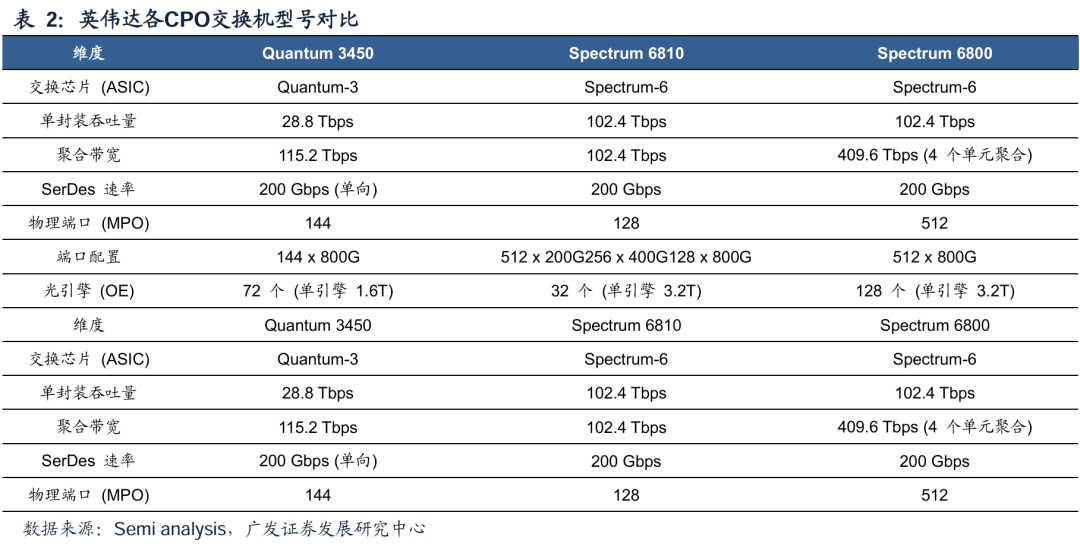

英伟达已发布两款CPO交换机Spectrum-X和Quantum-X。根据Semi analysis,英伟达GTC 2025上,英伟达首次推出了面向扩展网络的基于CPO的三款交换机,分别为Quantum X800-Q3450、Spectrum 6810和Spectrum 6800。根据微电子制造公众号,2026年3月英伟达正式发布两款硅光网络交换机Spectrum-X和Quantum-X。两款交换机适配不同场景,Spectrum-X用于以太网平台,适合多租户、超大规模AI工厂;Quantum-X用于InfiniBand平台,采用液冷设计。

Quantum 3450:该款CPO交换机拥有144个物理MPO端口,支持144个800G逻辑端口或72个1.6T逻辑端口,总带宽为115.2T,采用四颗28.8Tbit/s带宽的Quantum-X800 ASIC芯片,每个ASIC外围有六个可拆卸的光学子组件,每个子组件内含三个光引擎。

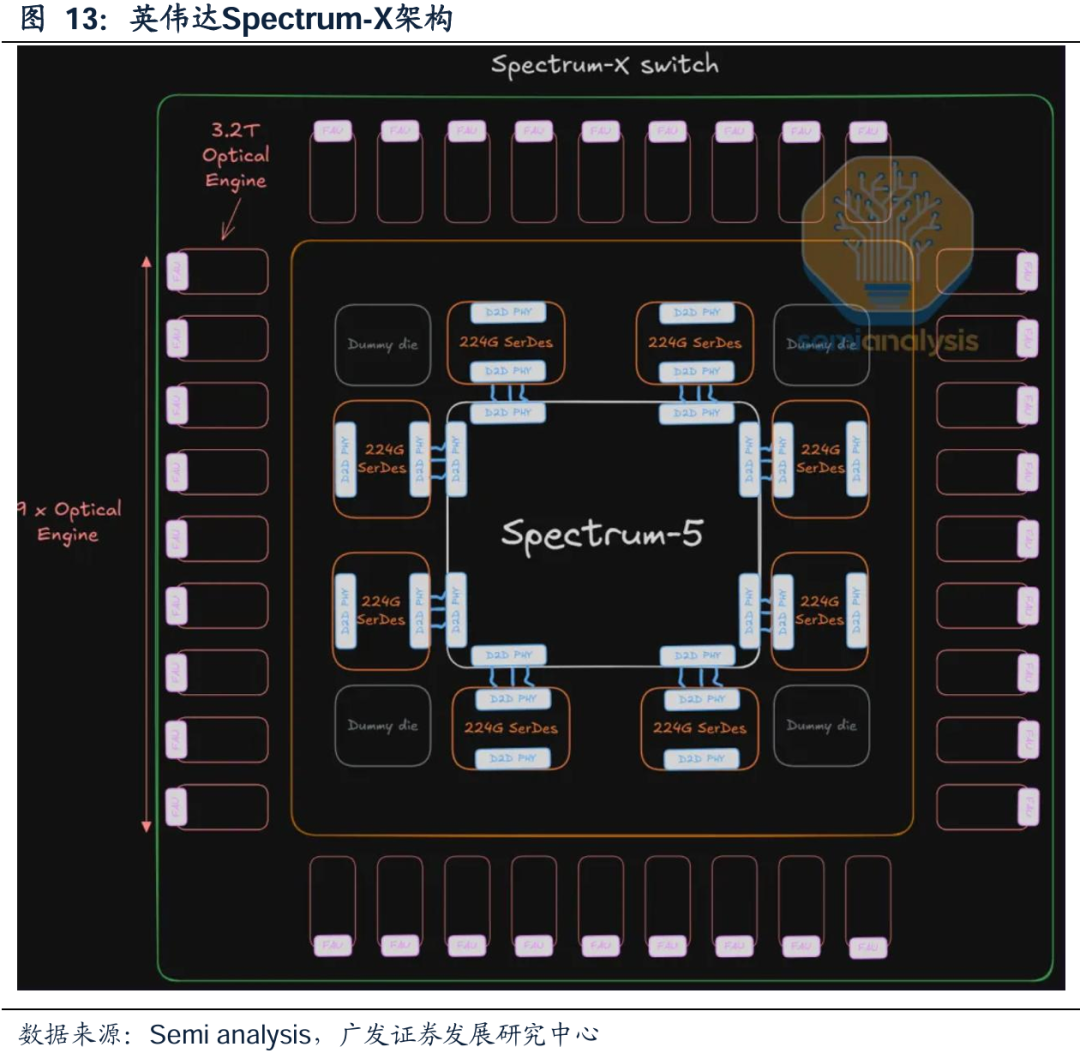

Spectrum-X:Spectrum-X Photonics平台代表CPO交换机技术的下一步演进,该产品线包括Spectrum 6810提供102.4T的总带宽和Spectrum 6800通过四封装设计提供409.6T带宽的两种配置。Spectrum-X不同于使用四个独立的单片交换封装的Quantum X800-Q3450,Spectrum-X采用多芯片模块,中心是更大的102.4T交换ASIC,周围环绕八个224G SerDes输入/输出chiplet,每侧两个chiplet。每个Spectrum-X光子多芯片模块交换封装在单个102.4T交换封装中集成36个光引擎。

Spectrum-X 6810交换盒使用一个多芯片模块封装单元来提供102.4T总带宽。更大的Spectrum-X 6800交换盒通过利用四个这样的Spectrum-X交换封装实现409.6T的总带宽,这些封装在多平面配置中连接到外部物理端口。

2. 博通:在CPO交换机领域布局较早

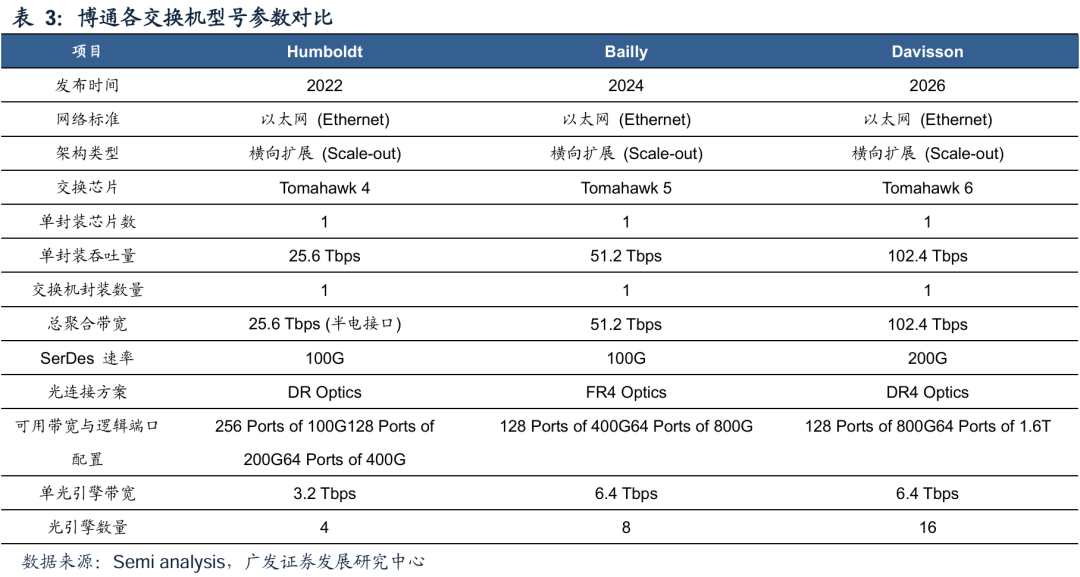

博通在CPO交换机领域布局较早,2022年就已推出首款CPO交换机。根据Semi analysis,博通第一代CPO器件称为Humboldt,基于Tomahawk 4交换ASIC,于2022年推出时主要作为概念验证。第二代CPO器件Bailly基于Tomahawk 5交换ASIC,在2024年推出。2026年,博通正在推出基于Tomahawk 6交换ASIC的Davisson CPO交换机。

Humboldt:第一代Humboldt系统配备25.6T以太网交换机,一半CPO一半电气连接,使用4个3.2T光引擎和32x100Gbps DR连接,光引擎是键合到SiGe EIC的光电子集成芯片,约有250个光学组件。

Bailly:第二代Bailly系统,配备51.2T以太网交换机,全光CPO连接使用8个6.4T光引擎和64x100Gbps FR4连接,光引擎是键合到CMOS EIC的光电子集成芯片,包含约1000个光学组件。

Davisson:Davisson以太网交换机的物理实现,配备开发的CPO 200G/lane PAM-4技术和16x 6.4T OE chiplet的DR光学配置。交换ASIC采用TSMC的N3工艺节点制造,每个封装提供102.4 T每秒的带宽。

3. Marvell:布局全栈式CPO技术体系,推出TX9190 CPO交换机

Marvell已布局全栈式CPO技术体系,最新推出TX9190 CPO交换机。根据Marvell官方Linkedin,公司在2025年OCP Summit展会上Marvell联合Jabil率先推出102.4T级CPO交换机参考设计,该CPO交换机采用模块化光学架构,具有可插拔光源和内部光纤布线功能,缩短电线长度,提高信号完整性;此外,TX9190将液冷直接集成到交换机架构中,围绕光纤通道集成液冷管,实现最佳散热管理。

二、CPO制备工艺及设备环节

(一)CPO涉及前道和后道两大工艺环节

根据《Silicon photonics CPO testing technology challenges》(Ching Cheng Tien,矽格股份),以英伟达的Quantum-X Photonic Switch为例,涉及到的工艺/技术有:

1. OE部分(Optical Engine,光引擎)

Photonic IC(光子集成电路,PIC):集成激光器、调制器、探测器等光器件,负责光信号的产生、调制与接收,是CPO的“光大脑”,也是CPO与传统的光模块技术相比,集成度提高的主要部分。

Electronic IC(电子集成电路,EIC):包括计算/交换芯片(如GPU、AI交换机芯片),负责电信号处理与算力执行。

3D Stacked Electronic and Photonic Ics & Coupe uLens(3D堆叠电子与光子集成电路 & Coupe 微透镜技术):将PIC和EIC通过3D堆叠技术封装在一起,提升互联带宽与集成度;以及微透镜耦合技术,用于高效连接光子芯片与光纤,降低光信号损耗、提升耦合效率。

Fiber Receptacle(光纤插座):光纤与设备的物理接口,用于固定、对接光纤,保障光信号稳定传输。

Fiber Connector(光纤连接器):实现光纤之间、光纤与设备之间的可拆卸连接,是光通信的基础接口部件。

Optical Sub-Assembly(光学子组件):整合透镜、光纤、耦合结构的核心光学部件,负责光信号的整形、传输与耦合。

2. 其他部分

External Laser Source Module(外部激光源模块,ELS):将激光器独立放置在设备外部,通过光纤将光传输至光子芯片,可优化散热、提升功率扩展性

Laser Source Package(激光源封装):激光器的封装载体,保护激光器芯片并实现电气连接与光信号输出。

Interposer(中介层):用于连接不同芯片(EIC/PIC/激光源芯片)的高密度布线层,实现芯片间的高速信号传输。

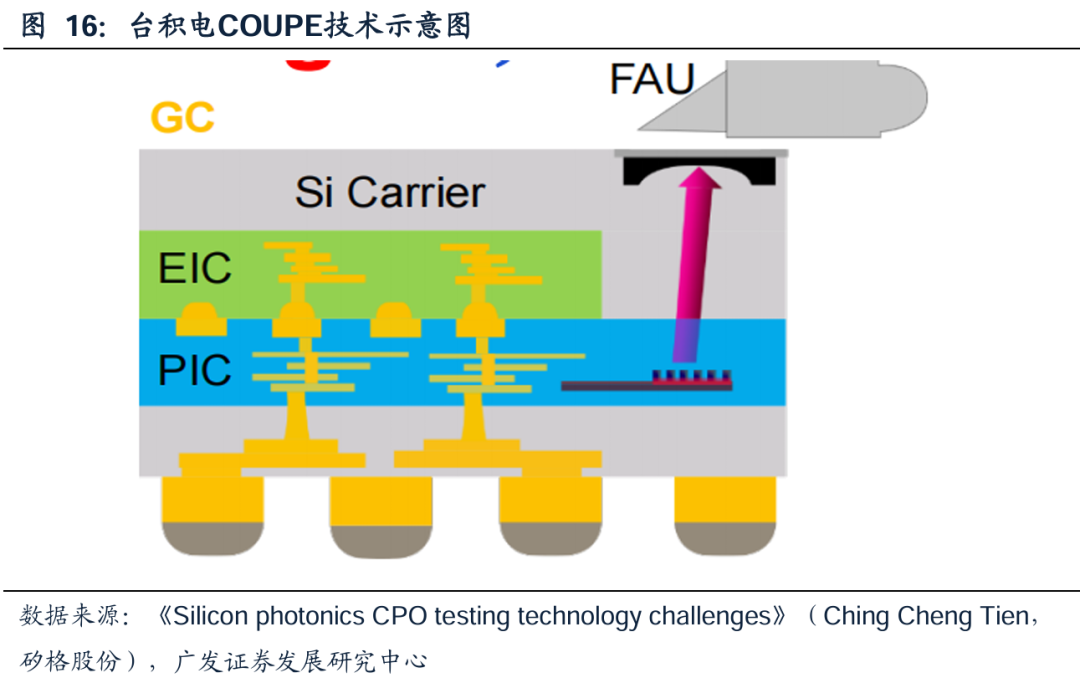

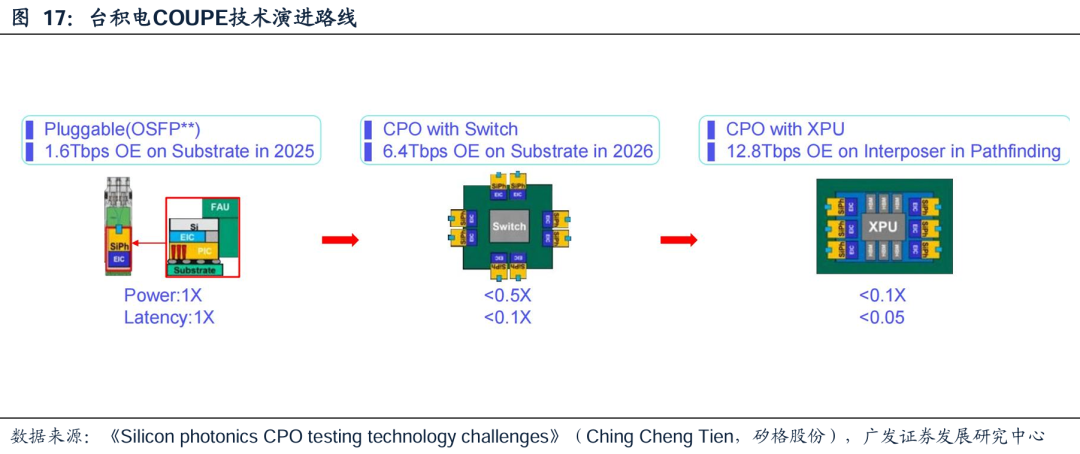

台积电COUPE(Compact Universal Photonics Engine,紧凑型通用光子引擎)技术。台积电的COUPE技术涉及到EIC、PIC、FAU的集成(GC,光栅耦合器),采用SolC-X工艺实现EIC-on-PIC堆叠,按照台积电的路线图,COUPE分作3个阶段,大致方向是离核心芯片(XPU)越来越近,当然技术挑战也越来越大:

1.可插拔级别。在可插拔OSFP光模块中部署COUPE,实现1.6T bps光引擎连接。

2.交换机级别的CPO。在CoWoS基板级CPO中部署COUPE,功耗降低2倍、延迟降低10倍,主要应用于光引擎和交换芯片的CPO。

3.XPU级别的CPO。在CoWoS中介层上部署COUPE,功耗再降5倍、延迟再降2倍,直接实现光引擎与计算核心的CPO,极致逼近算力核心。

CPO的工序较为复杂,涉及到多个主体之间的配合,而且测试工序较多:

1.FAB端:Foundry主要负责完成EIC/PIC的测试、3D堆叠与微透镜集成,主要涉及EIC Wafer的制作和测试、PIC Wafer的检查与清晰、PIC Wafer的光学分选、晶圆减薄/3D SoIC键合/COUPE 微透镜集成、双面晶圆微透镜检查与清洗、以及双面晶圆测试。

2.光学组装:光学组装环节将堆叠晶圆切割为光引擎,并完成光纤接口装配与测试,主要涉及光引擎芯片的切割、光引擎微透镜检查与清洗、光纤插座的装配(光纤插座与光引擎芯片连接)、光引擎-光纤插座组件检查与清洗、以及光引擎封装测试。

3.封装:CPO组装环节将光引擎与ASIC共封装,最终完成系统级验证,包括ASIC(交换芯片、XPU等)与光引擎的CPO共封装、CPO光纤连接器检查与清洗、CPO的系统级测试(SLT)。

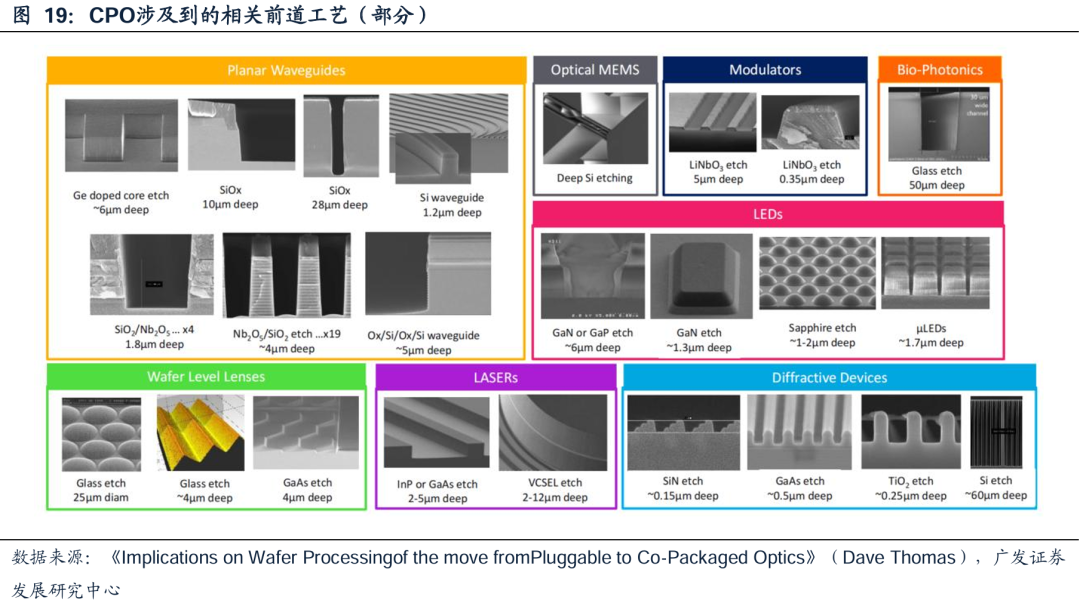

(二)CPO前道涉及到多种工艺设备

CPO涉及多种前道工艺。根据《Implications on Wafer Processingof the move fromPluggable to Co-Packaged Optics》(Dave Thomas),CPO由于涉及到“光”器件的相关功能实现,其中涉及到:

1. Planar Waveguides(平面光波导)。光波导是PIC的“导线”,涉及到Ge、SiOx、Si光波导的刻蚀,以及SiO2/Nb2O5、Nb2O5/SiO2、Ox/Si/Ox/Si波导等的沉积和刻蚀;

2. Optical MEMS(光学MEMS)。主要是用来调控光器件,核心工艺是深硅刻蚀(Deep Si etching)。

3. Modulators(光调制器)。光发射端的核心器件,涉及到薄膜铌酸锂(LiNbO₃)的刻蚀。

4. Wafer Level Lenses(晶圆级透镜)。CPO中光引擎(OE)的重要组成部分,是OE的核心光学接口,涉及到Glass以及GaAs(砷化镓)的刻蚀。

5. LASERs(激光器)。激光器是CPO的核心有源器件,涉及到InP/GaAs、VCSEL(垂直腔面发射激光器)的刻蚀。

6. Diffractive Devices(衍射光学元件)。硅光芯片的光输入输出接口,主要有SiN的刻蚀。

总的来看,硅光波导(PIC)、铌酸锂调制器、激光器(EEL/VCSEL)、光栅耦合器、微透镜阵列,所有CPO的核心组件均涉及到相关的薄膜沉积以及刻蚀工艺。

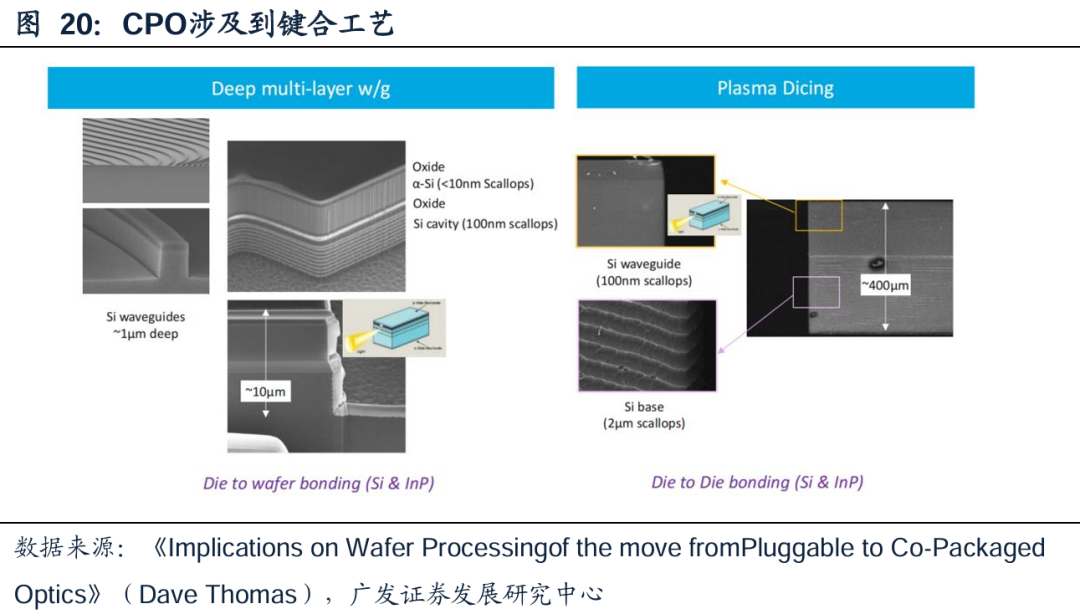

(三)CPO后道涉及到键合、TSV等工艺

CPO涉及到EIC和PIC晶圆的键合以及切割。Deep multi-layer w/g(深多层波导 / 腔体)为CPO异质集成的前道工艺,将InP(磷化铟)激光器芯片批量键合到硅光晶圆上,为“硅光 PIC(无源层) InP激光器(有源层)”的片对晶圆(Die-to-Wafer)异质集成,为光引擎PIC层的核心制造工艺;

Plasma Dicing(等离子切割),替代传统机械切割,用于硅光/CPO晶圆的芯片切割,避免机械应力导致的芯片损伤、翘曲,支撑片对片(Die-to-Die)键合。

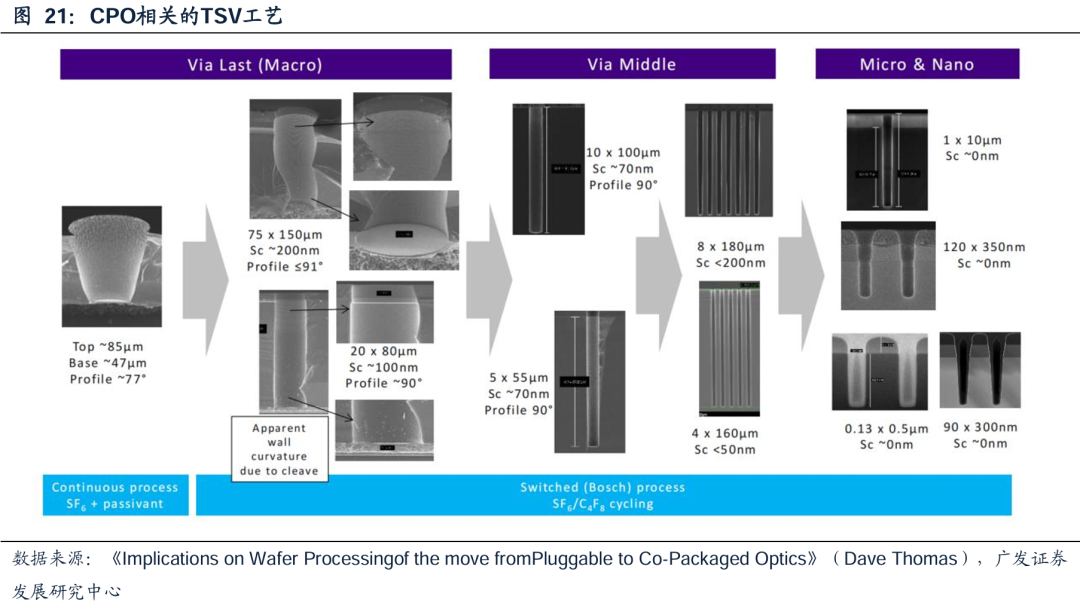

TSV(硅通孔)工艺。在CPO的3D堆叠中,TSV替代长距离主板布线,将电信号路缩短为 “封装内垂直互联”,可以实现降低功耗、降低延迟的效果。

(四)光电测试是CPO中的主要难点之一

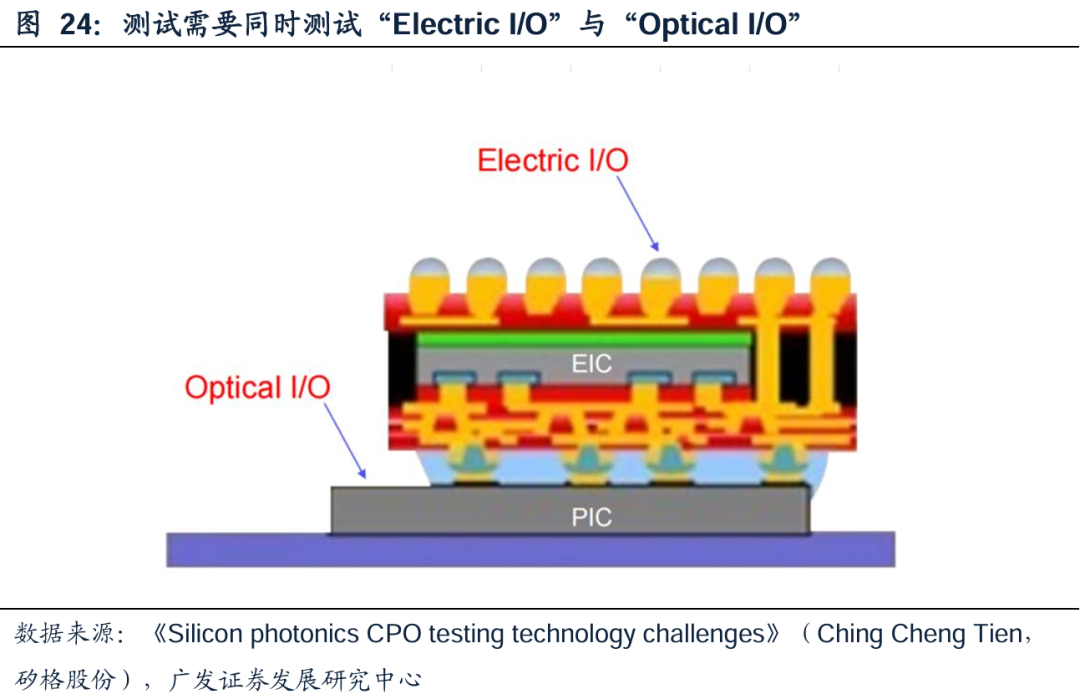

CPO的测试涉及光与电的测试。传统的半导体测试,一般只涉及电的测试,这方面已经比较成熟,而CPO因为同时集成了EIC与PIC,需要叠加“光”方面的测试,而本身PIC是不发光的无源器件,测试难度也就相应加大,涉及到了测试机、探针卡、耦合模块、标准测试仪器的开发。

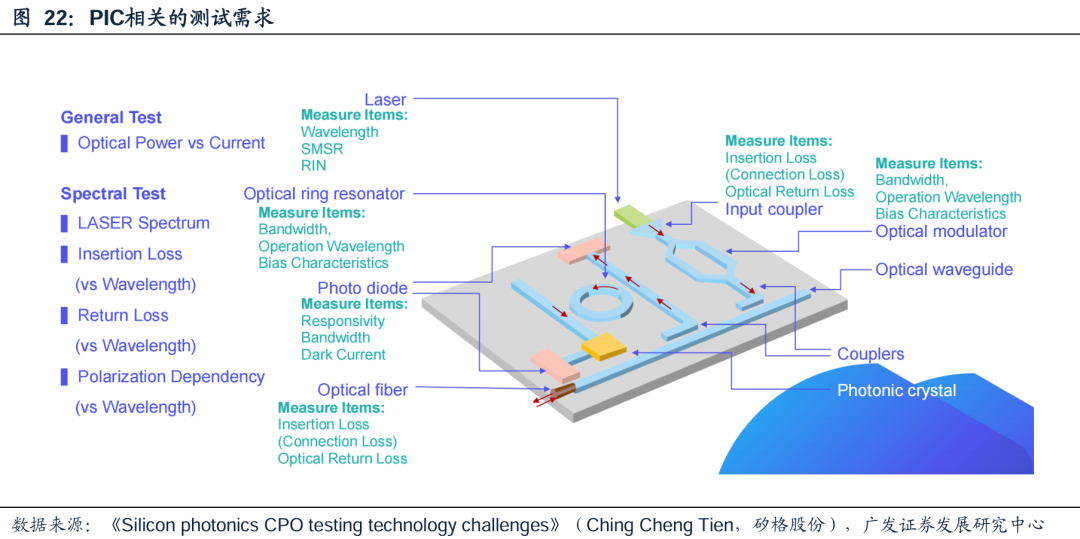

以PIC的测试为例,除去通用测试以外,还涉及到光谱测试,包括激光器的光谱测试(LASER Spectrum)、插入损耗(Insertion Loss)、回波损耗(Return Loss)、偏振测试(Polarization Dependency),具体来看要对激光器、环形谐振器(Optical ring resonator)、光电二极管(Photo diode)、光纤(Optical fiber)、耦合器(Input coupler和Couplers)、光调制器(Optical modulato)、光波导(Optical waveguide)以及光晶体(Photonic crystal)的多项目测试。

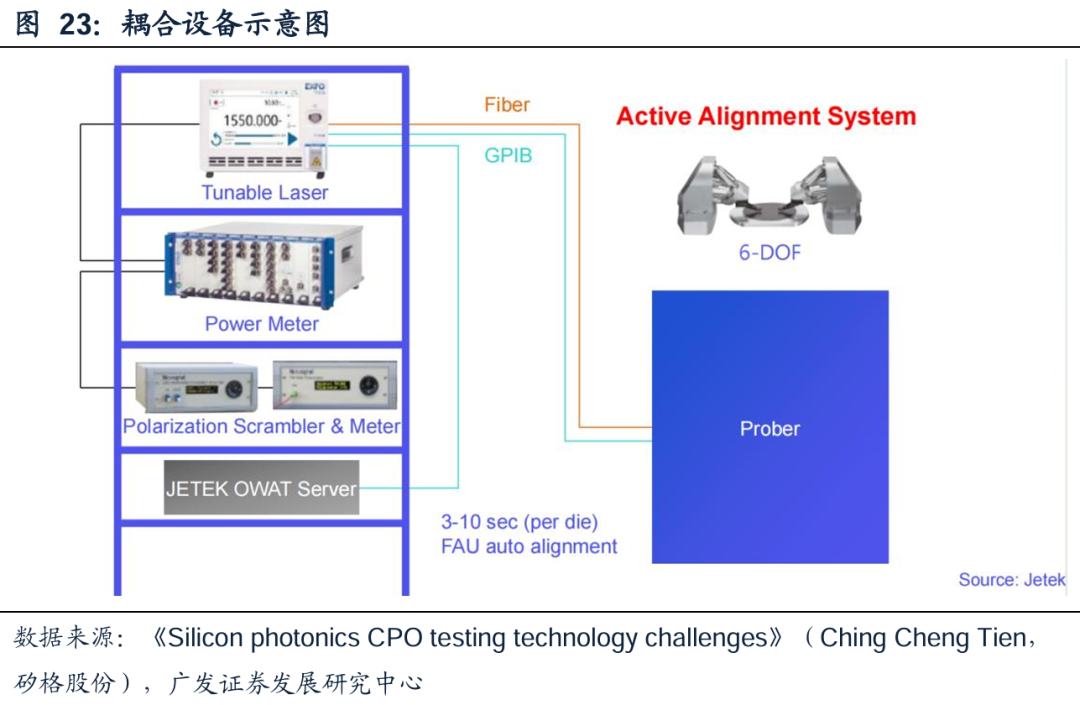

核心耦合设备。Tunable Laser(可调谐激光器)提供连续光信号,作为硅光芯片 / 光模块的输入光源;Power Meter(光功率计)实时监测光纤耦合后的输出光功率,作为对准的反馈信号;Polarization Scrambler & Meter(扰偏器与偏振计),扰偏器随机化输入光的偏振态,模拟实际光纤链路的偏振变化,验证耦合的偏振无关性,偏振计监测光的偏振状态,确保不同偏振下的耦合效率稳定;Active Alignment System(有源对准系统)核心为6-DOF六自由度精密位移平台,可实现亚微米级的位置调整负责夹持光纤,根据OWAT Server的指令,动态调整光纤与硅光芯片波导的相对位置。

三合一设备或成未来主流。根据ficonTEC官方Linkedin,公司在25年3月宣布推出ficonTEC&泰瑞达Teradyne& Femtum三方联名开发的设备,即晶圆级双面“光电”测试 激光清洁 激光修复三合一设备。最左边是泰瑞达机台,作为全球半导体测试机的龙头,主要负责在对封装晶圆进行高频电信号的测试,中间则是ficonTEC机台,需要在电信号接通的同时完成光的测试,最右则是Femtum的激光清洁与修复模块,对测试环节发现的缺陷,进行激光修复。

风险提示

(一)CPO技术迭代进度不及预期

CPO技术目前仍处于产业化早期阶段,具体工艺、流程、产线设备等均未定型。若CPO技术因散热难题、良率瓶颈、标准化协议未统一或生态成熟度不足等原因,导致其商业化落地时间大幅推迟,从而导致相关企业受到短期冲击。

(二)全球AI基础设施建设投资整体降温

若全球地缘政治摩擦加剧导致供应链割裂、各国针对AI芯片及数据中心的监管政策收紧、或生成式AI商业模式证伪导致行业进入去泡沫化阶段,均可能引发全球AI基建投资周期的下滑。

(三)竞争格局恶化风险

CPO制造工艺技术迭代较快,若设备厂商未能及时跟进最新工艺研发,导致技术方案落后,或行业新进入者引发激烈的价格战,可能导致公司毛利率下滑及市场份额流失。

VIP复盘网

VIP复盘网