在AI算力呈指数级爆发的时代,数据中心的每一秒都在吞吐海量信息。当网络架构从800G向1.6T乃至3.2T狂飙,单通道PAM4信号速率突破112Gbps并加速迈向224Gbps,物理层的传输正逼近极限。此时,时钟源的每一飞秒(fs)抖动,都可能成为吞噬信号裕量、让数据传输“误入歧途”的致命因素。

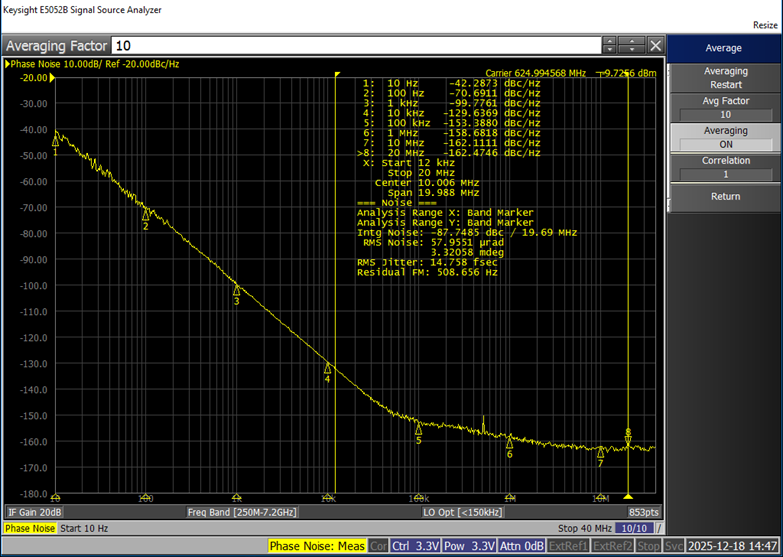

针对这一行业痛点,泰晶科技发布625MHz超低抖动差分晶振。该产品采用自主研发的光刻高基频(High-Frequency Fundamental)晶片技术,实现625MHz真基频输出,在12kHz~20MHz积分区间内,相位抖动低至惊人的15fs(典型值)。这款产品为下一代DSP、SerDes提供了“一次成型”的纯净参考时钟,从源头上彻底消除了传统锁相环(PLL)倍频引入的杂散与相位噪声抬升。

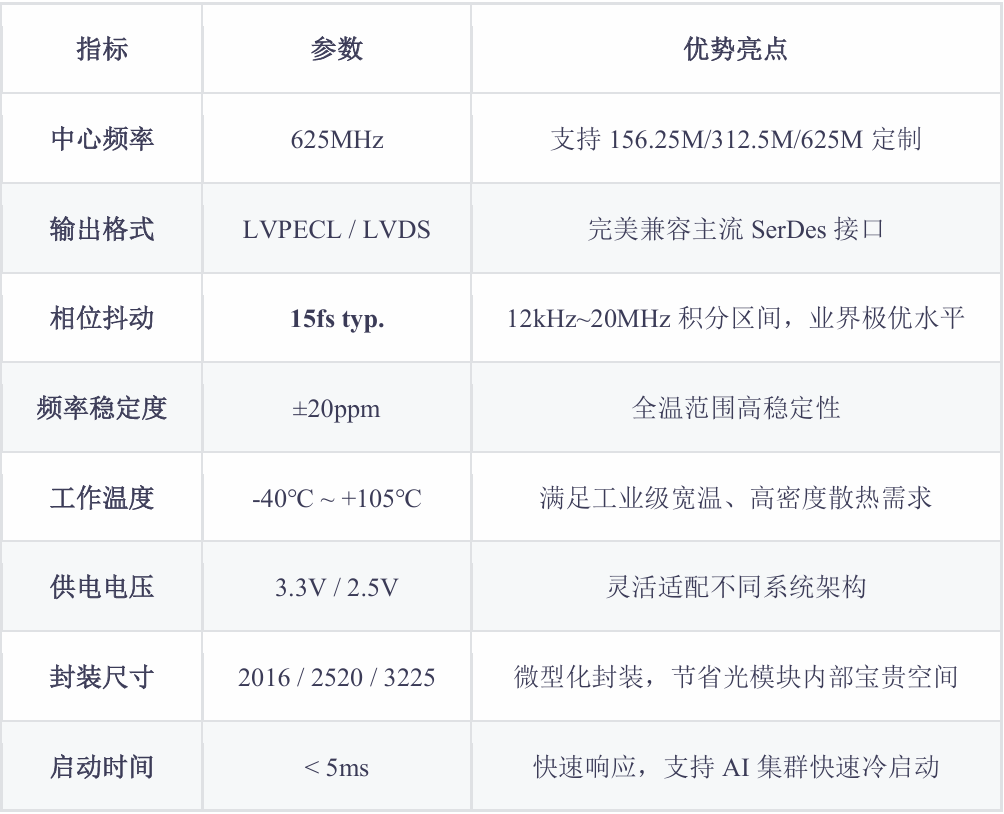

核心性能指标概览

剑指224G:

为单波400G量身打造的“时钟引擎”

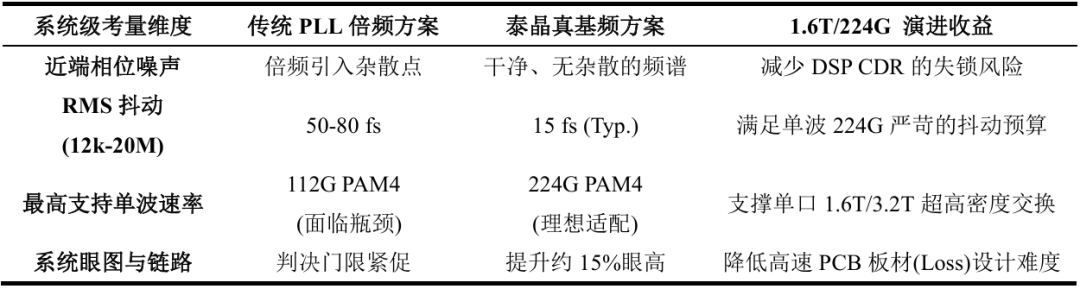

在光通信向1.6T/单波400G(224Gbps PAM4)演进的征途中,传统的156.25MHz或312.5MHz倍频时钟方案已触及物理极限。

● 守护苛刻的抖动预算(Jitter Budget):

在224G单波方案中,信号的单位间隔(UI)极窄,仅约8.9ps。泰晶科技625MHz差分晶振提供的15fs超低抖动,仅占极微小的UI周期(约0.17%)。这为经过高损耗背板或复杂光电转换后的信号,保留了至关重要的抖动预算,确保DSP能够精准采样和恢复数据。

● 625M真基频直驱:

在1.6T(8x200G或4x400G)架构下,系统参考时钟频率上移至625MHz已是主流趋势。泰晶科技真基频技术避免了跨时钟域带来的不稳定因素,极大降低了DSP内部CDR(时钟数据恢复)失锁的风险。

15fs超低抖动:

转化为实实在在的系统级红利

15fs的极低抖动与优异的相位噪声表现(10MHz偏移处底噪优于-160dBc/Hz),不仅是参数表上的数字,更能转化为显著的系统级优势:

● 显著提升Pre-FEC信噪比余裕

在高速PAM4链路中,泰晶科技15fs差分晶振相比传统50fs产品,可有效改善发射端(Tx)的信号完整性。极纯净的时钟显著提升了Pre-FEC(纠错前)系统的信噪比余裕,为接收端DSP算法提供了更宽广、更清晰的判决窗口,确保系统长期运行的稳健性。

● 增强复杂链路与环境的适配能力

超低抖动有效补偿了高速链路中的确定性抖动,使得光模块Tx端眼图张角提升约15%。这一性能增益极大增强了光模块对高损耗PCB板材的宽容度,在面对海底光缆、长距干线网络及高密度插拔场景时,展现出更强的连通能力。

● 优化CDR压力与系统动态功耗

极致的低抖动时钟输入,意味着无需依赖DSP/SerDes内部进行极其复杂的抖动消除算法。这直接减轻了均衡器(如FFE/DFE)的抽头负担和CDR电路的处理压力,从而有效优化了芯片组的动态功耗,缓解了1.6T高密度光模块面临的严峻散热挑战。

从晶振到系统,专业级性能对比

赋能极速未来:典型系统级应用

● 1.6T/3.2T 高端光模块:

为核心DSP和Driver驱动芯片提供625M基频参考,消除杂散,支撑单波224G PAM4信号的极限传输。

● AI计算集群与高速交换:

为超算内部的高速私有协议互连、NVLink及下一代以太网交换芯片提供超低抖动参考时钟。

● 相干光通信与高阶互连:

极低的相噪底(Floor)完美契合相干光通信中高阶调制(如16QAM/64QAM)的需求,极大优化EVM(误差矢量幅度)性能。

● 高频雷达与测试测量:

确保多通道相控阵雷达波束合成的极高相位一致性;同时保证高端示波器ADC采样精度逼近理论极限。

在光电互连日趋极限的今天,泰晶科技通过底层材料与光刻工艺的突破,正在为全球高速网络基础设施提供坚如磐石的“国产纯净芯”。

VIP复盘网

VIP复盘网