核心观点

自主可控与AI算力驱动,国内半导体制造迎重大机遇:为满足人工智能领域不断增长的算力需求,全球GPU芯片的需求量大幅提升。美国针对GPU芯片对华出口的管制日趋严格;国内GPU企业在中国大陆以外的晶圆代工渠道也面临着更多风险。自主设计 代工生产的国产GPU芯片已成为保障国内人工智能产业发展的关键替代品,其生产过程需要消耗大量的晶圆代工产能。中芯国际等企业有望满足此需求,实现工艺技术与营收规模的双重突破。

先进制程产线扩产设备需求旺盛,国产设备有望不断壮大:GPU芯片生产主要采用先进制程工艺,所需的半导体设备价值金额更大,性能也更先进。美欧日限制高端半导体设备对华出口,反而为国产设备带来更多验证和测试的机会。国内半导体设备企业近年来技术不断取得突破,有望在后续新建的芯片产线中取得更高的份额,从而实现业绩的快速增长。

新兴技术助力国内晶圆制造攀登巅峰:受制于物理极限,先进制程晶圆制造技术的发展逐步放缓;国内先进制程技术研发更受制于荷兰光刻机出口限制。但是随着多重图形化、三维异构、新型晶体管结构等新技术逐步得到重视,中国大陆面临的“光刻瓶颈”难题有望得到部分解决,从而助力国内晶圆制造行业竞争力迈上新台阶。

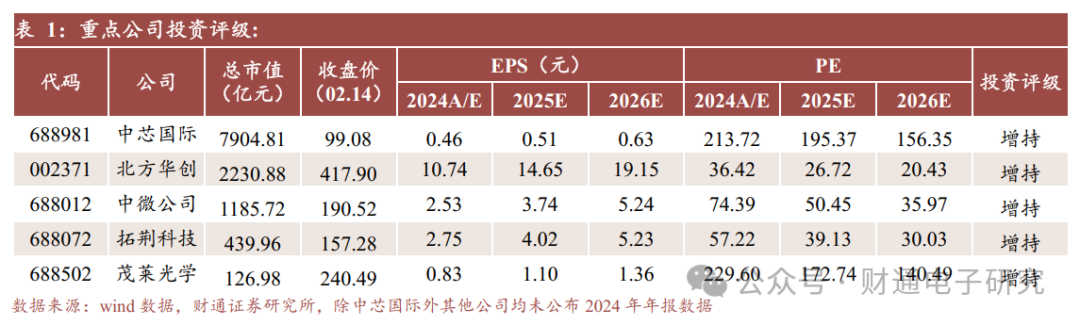

投资建议:建议关注中芯国际、北方华创、中微公司、拓荆科技、茂莱光学等国内半导体领域企业。

风险提示:半导体需求不及预期;技术研发不及预期;海外供应链风险;行业竞争加剧。

内容目录

1芯片生产:多重因素密集催化,国内半导体制造产业迎来关键转折点

1.1人工智能发展日新月异,半导体制造产能需求量激增

2迎难而上突破封锁,国内晶圆代工有望乘人工智能东风

2.1多重图形化技术,有望暂时解决燃眉之急

2.2三维异构技术:另辟蹊径规避部分物理瓶颈

2.3新型晶体管结构与材料,有望带来革命性变化

2.3.1GAA技术助力先进逻辑制程发展

2.3.23D DRAM技术助力内存产业突破原有极限

3投资建议:

3.1晶圆代工:国内晶圆代工需求有望持续增长

3.2半导体设备:半导体供应链上游基石

3.3半导体材料与零部件企业:半导体供应链的血液

4风险提示

1

1 芯片生产:多重因素密集催化,国内半导体制造产业迎来关键转折点

1.1 人工智能发展日新月异,半导体制造产能需求量激增

随着人工智能产业的快速发展,AI相关的云端(服务器)和终端(AIPC、AI手机)产品出货量快速增长,产生大量高端芯片需求。受AI需求驱动,全球半导体销售金额在2023年2月触底后迅速回升; 2024年11月全球半导体销售金额达578.2亿美元,创历史最高值。

GPU芯片主要应用于AI服务器,是目前人工智能领域需求最为迫切的芯片。 GPU芯片具备强大的并行计算能力,内部包含大量的计算单元,能够同时处理多个任务,使得其在处理大规模数据方面具有显著优势。在科学计算领域,GPU芯片能够加速模拟和仿真过程,提高计算效率。AI手机与AIPC在端侧运行AI应用,需具备更强大的运算能力,故其芯片性能和设计也有相应的升级。

AI手机芯片方面,以苹果iPhone 16的A18 Pro芯片为例,神经引擎(NPU)为16核,算力为35 TOPS,约为A11芯片算力的58倍。高通、联发科也发布了新型的AI手机SOC芯片。AIPC芯片方面,AMD发布了新的AIMax和AIMax 芯片,能够满足从高端工作站到轻薄笔记本的广泛需求;英特尔也为AIPC推出了Ultra 200 系列芯片。

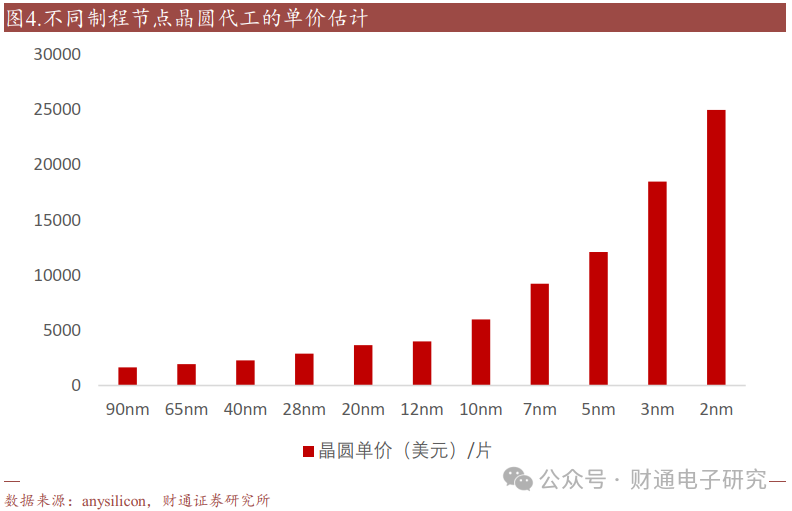

人工智能领域所需要的高端芯片多数采用先进制程。以英伟达公司的H100型GPU芯片为例,其采用台积电先进的4纳米制程,拥有超过800亿个晶体管。而苹果公司的A18 Pro芯片则采用3nm制程,拥有约200亿个晶体管。先进制程晶圆代工的价格也十分高昂,3nm节点的晶圆价格接近20000美元/片。人工智能领域需求的快速增长,推动了先进制程晶圆代工技术水平和收入的提升。

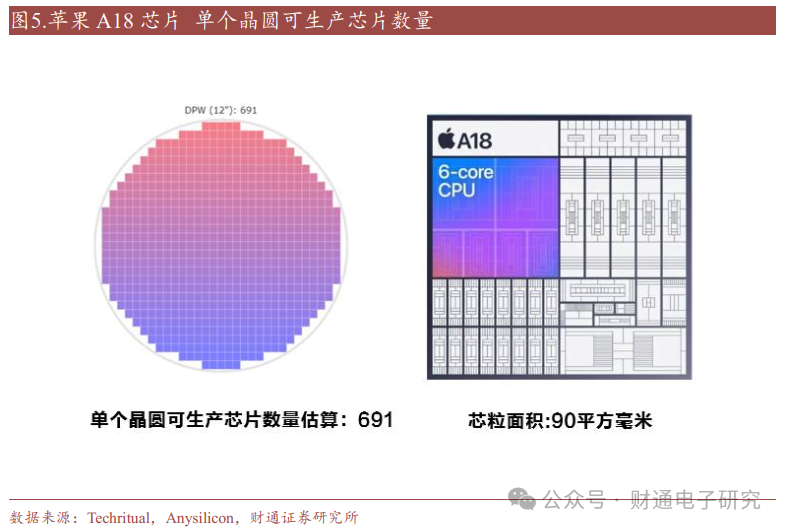

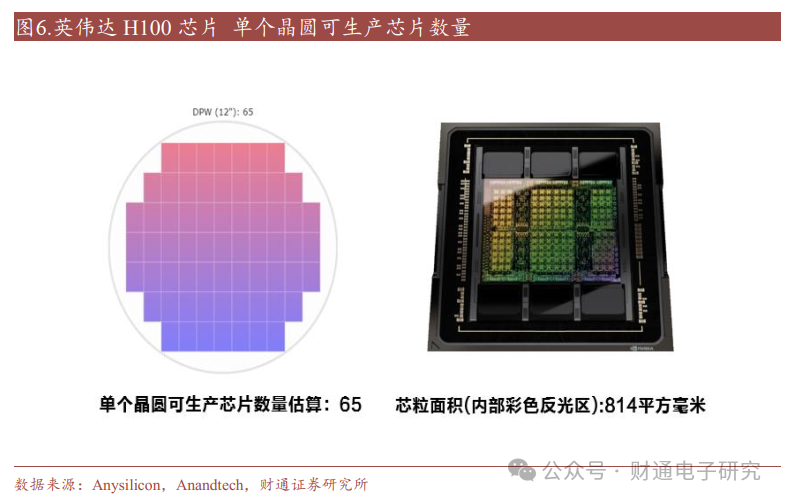

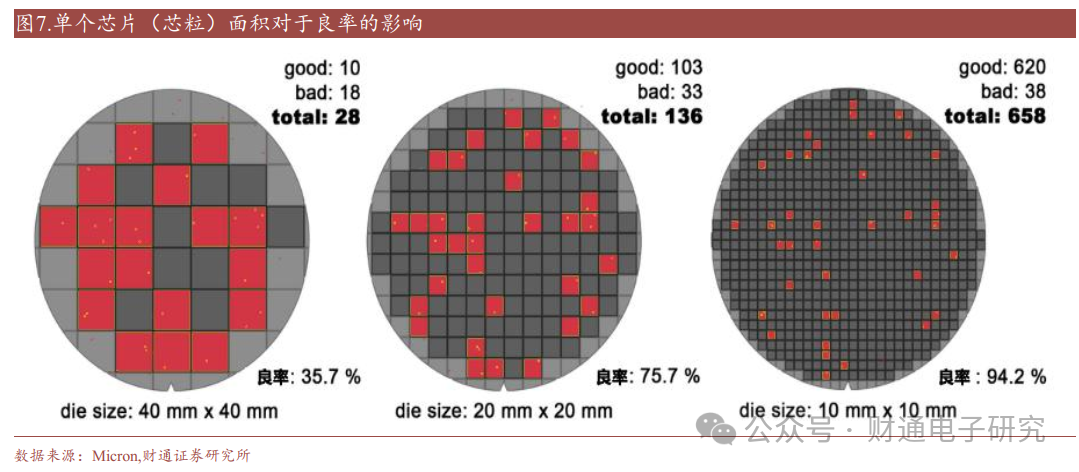

此外,与智能手机所用芯片相比,服务器使用的GPU芯片面积通常较大。英伟达H100芯片的芯粒面积为814平方毫米,而苹果A18芯片的芯粒面积约为90平方毫米。芯片的形状通常为矩形;GPU芯片较大的面积,导致其生产过程中的晶圆面积利用率较低,单个晶圆上可生产出的芯片数量也较少。

据anysilicon估计,若采用12英寸标准晶圆,一片晶圆可生产A18 pro芯片约691个,如果生产H100芯片则只能产出约65个。此外,由于H100等GPU芯片单个芯粒的面积更大,工艺难度较高,其良品率也相对较低。

综上,生产高端GPU芯片会消耗大量的先进制程晶圆产能。受此影响,先进制程晶圆代工企业台积电的HPC(高性能计算)领域客户需求旺盛,贡献了公司大多数营收;其2024年Q4季度单季的HPC领域收入占比为53%,远超排名第二的手机领域(35%)。

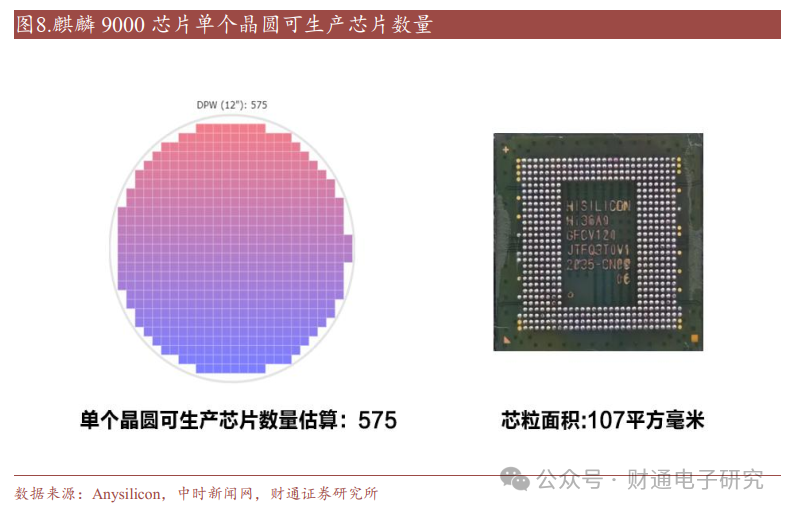

相比于海外领先企业的产品,国产高端GPU与手机芯片,其尺寸大小存在一定差别。国产手机芯片以麒麟9000为例,其面积约为107平方毫米,略大于苹果A18芯片;而国产GPU芯片昇腾910B的面积为665.61平方毫米,面积小于英伟达的H100芯片。

造成这些尺寸差别的主要原因为芯片设计与工艺水平的差别。昇腾910B和设计与英伟达H100仍存在代差,下一代国产GPU昇腾910C对标H100芯片,尺寸有望更接近。此外。由于中国大陆的芯片制造工艺仍然落后于国际最先进水平,芯片的晶体管密度略低,故生产同样晶体管数量的芯片,单个芯片面积通常更大,消耗的晶圆代工产能更多。

2

2迎难而上突破封锁,国内晶圆代工有望乘人工智能东风

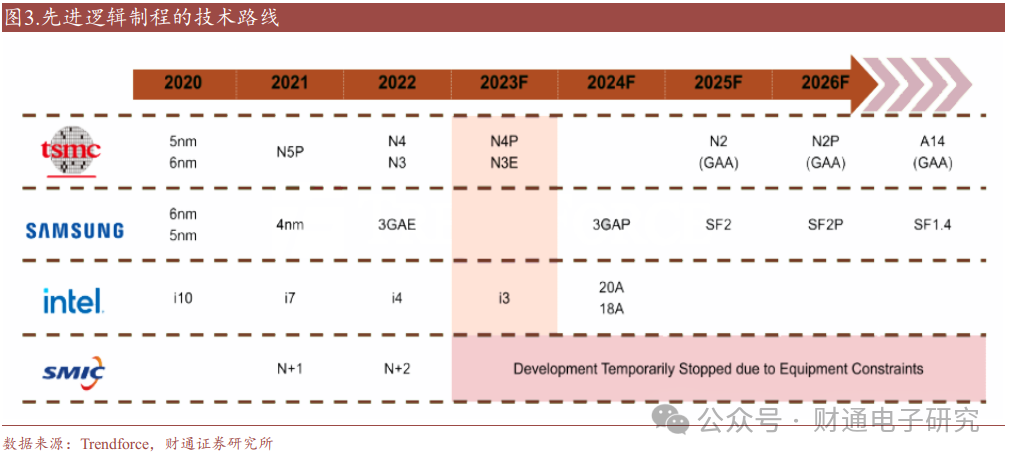

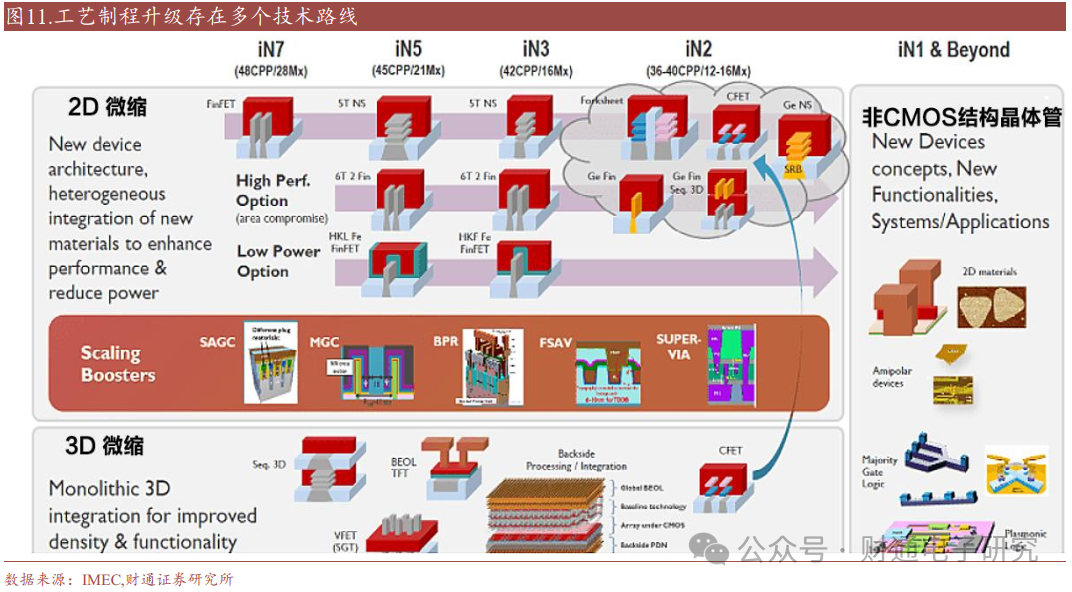

生产人工智能GPU芯片所需的先进逻辑制程晶圆代工产线,和生产HBM芯片的先进DRAM产线,需要极紫外(EUV)光刻机。但是由于荷兰拒绝出口EUV光刻机,中国大陆在7nm及以下逻辑芯片,1znm及以下DRAM芯片的生产过程中面临瓶颈。

由于极紫外(EUV)光刻机的供应限制,及其采购和使用的高昂成本,中国和海外企业积极寻求其的替代方案。新工艺、三维异构/先进封装、新材料、新型晶体管结构在内多种替代方案应运而生,为中国半导体产业在缺乏极紫外光刻机的条件下继续提升工艺制程创造了可能。

1.1 多重图形化技术,有望暂时解决燃眉之急

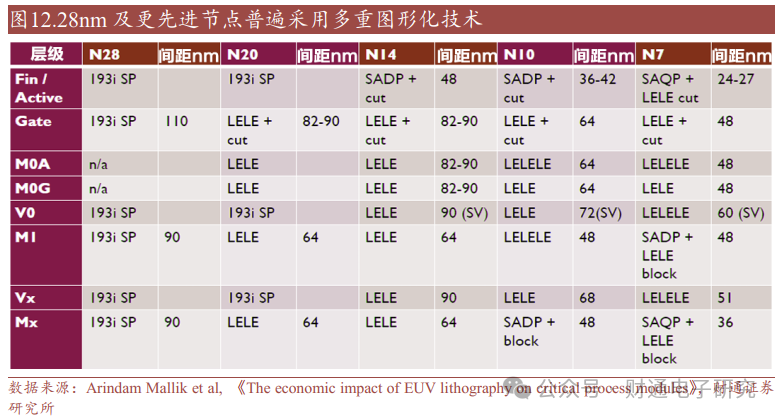

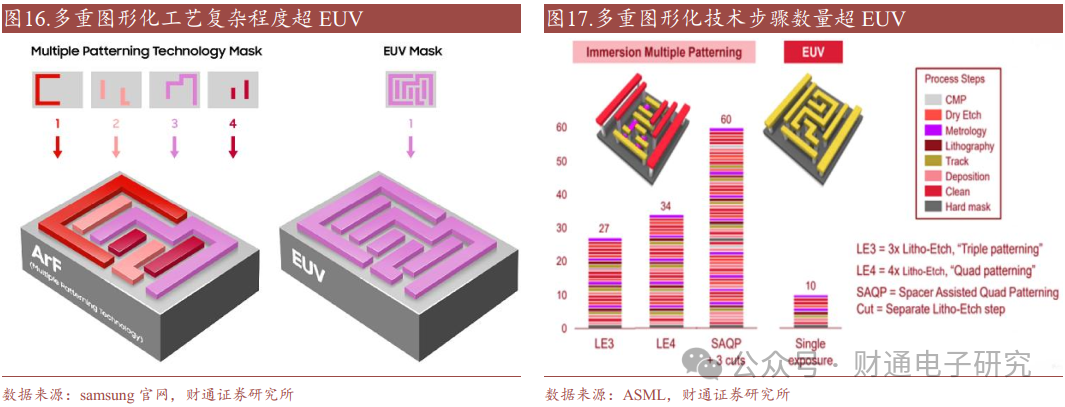

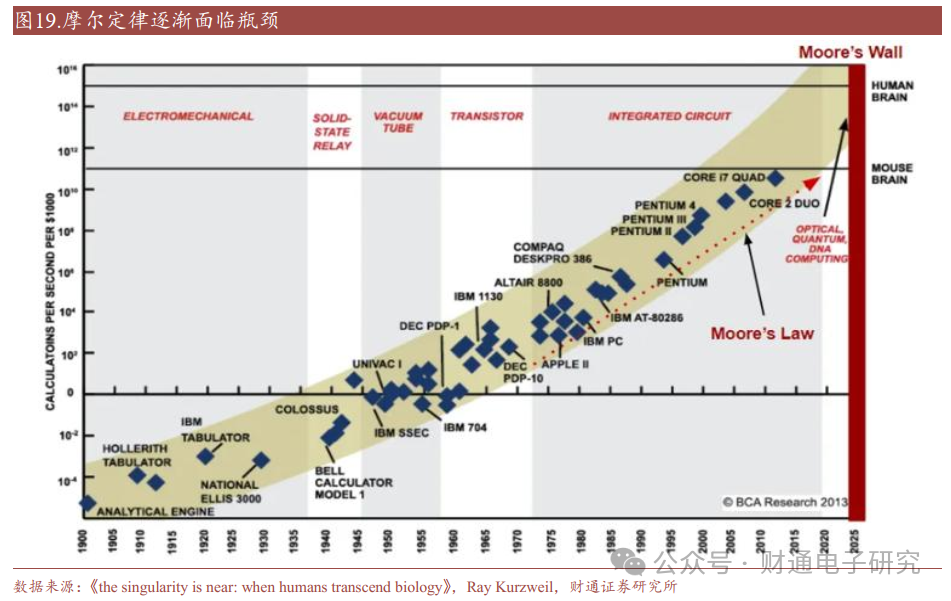

采用193nm光源的DUV光刻机,其极限分辨率为38nm;故集成电路中微小结构成型,通常需要使用多重图形化技术。多重图形化技术主要包括:自对准多重图形(SAQP/SADP)、多重曝光刻蚀(LELE/LELELE)两大类。在缺乏EUV光刻机的条件下,多重图形化技术,未来有望广泛应用于中国大陆的先进制程产线。

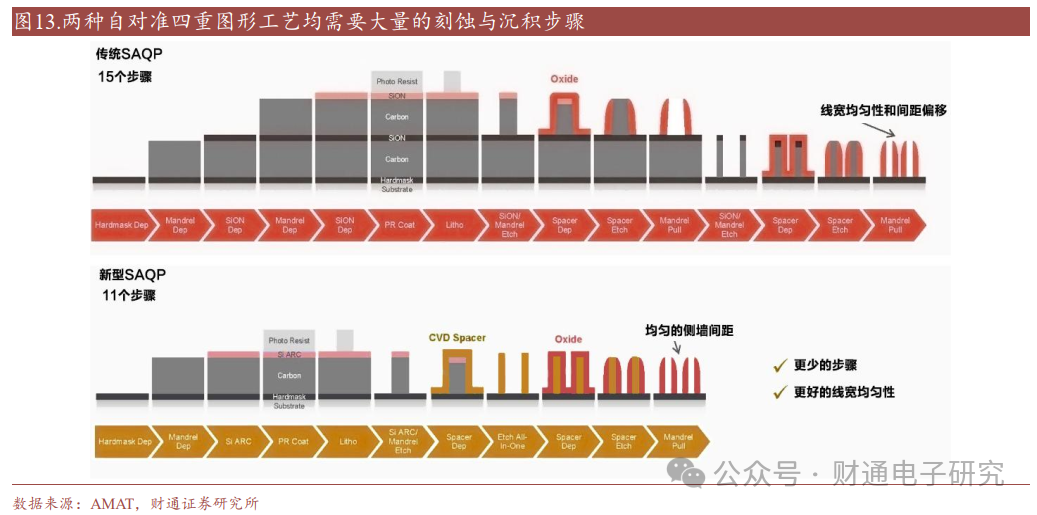

SAQP全称Self-Aligned Quadruple Patterning,即自对准四重成像技术,它是一种在晶圆上进行多次蚀刻和薄膜沉积,以增加晶体管密度从而提升芯片性能的技术。

SADP技术先利用浸没式光刻机形成节距较大的线条结构,再使用刻蚀设备和薄膜沉积设备,通过侧墙图形转移的方式,每次形成间距为原先1/2的线条结构。SAQP技术比较适合线条排列规则的图形层,如FinFET工艺中的Fin或后段金属线条。SADP技术由于对光刻套刻对准的精度要求较低,故降低了对光刻机的要求;但增加了对设计图形的限制,对刻蚀设备和薄膜沉积设备也有较高的要求。

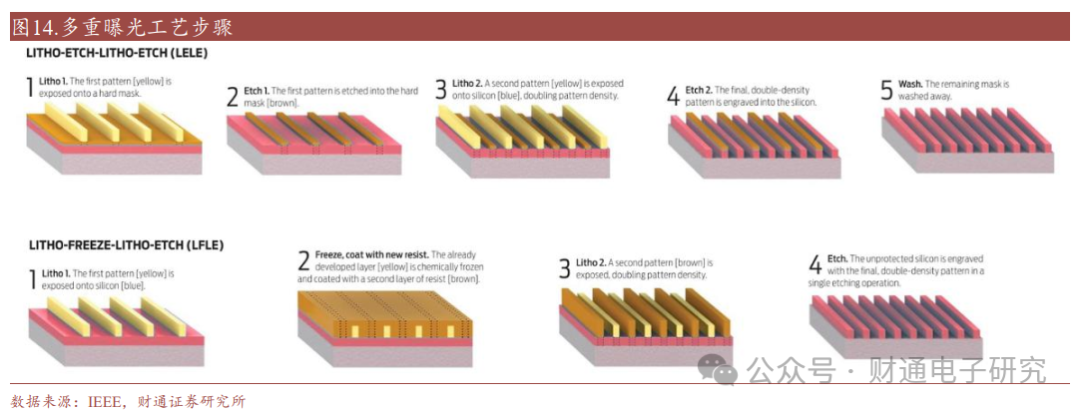

除自对准多重图形外,多重曝光技术也是先进制程技术攻关的一大利器。多重曝光光刻工艺是将版图图案分解到多张不同的掩膜版上,通过多次曝光和刻蚀的迭代过程,最终形成完整的硅片图案。如何将GDSII设计版图图案分配到多张不同的掩膜版上,使得在同一张掩膜版上的图案冲突最少,是多重曝光版图分配方法的关键;

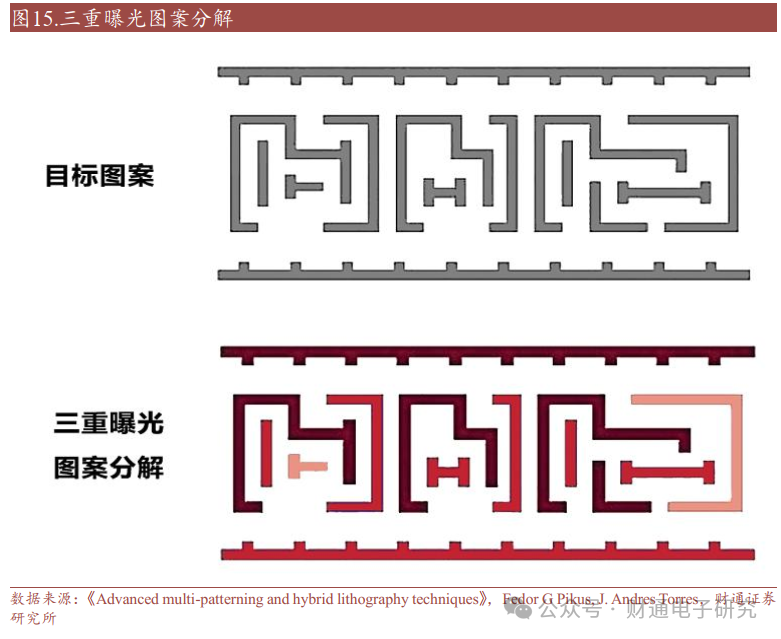

在20/22纳米工艺技术节点中,双重曝光光刻工艺已得到广泛应用。但在14/16纳米工艺技术节点,随着集成电路特征尺寸的进一步缩小,版图图案更加密集,开始引入三重曝光光刻技术。三重曝光通常使用曝光-刻蚀-曝光-刻蚀-曝光-刻蚀(LELELE)工艺进行生产。

三重曝光(LELELE)技术将线条密集的目标电路图案,分解成三个独立的较不密集图案。接着采用三个独立的光罩,通过光刻将三个较不密集的独立图案,转移到晶圆上。这项技术可有效降低光刻工艺的复杂性,提高分辨率水平,能够形成尺寸更小的图案;但是由于其涉及多次光刻步骤,存在过程繁琐、成本高、周期长、套刻精准度难以控制等问题。

由于多重图形化技术的所需的光刻、刻蚀、沉积等步骤数量较多,其在7nm节点往后遇到了良品率较低和成本较高的问题。台积电、三星等国际领先晶圆代工企业,在7nm节点以后开始大量使用EUV光刻技术取代使用DUV光刻的多重图形化技术。

针对中国大陆继续使用DUV光刻机 多重图形化技术生产比7nm更高端制程的可能性,台积电前研发副总监,浸没式光刻技术奠基人林本坚表示,依托现有的浸没式DUV光刻机,通过四重曝光制造出5nm芯片依然是可行的;后续最多可以通过六重曝光模式,实现更先进的工艺。然而,在使用 DUV 机器时,在多次曝光期间需要精确对准,需要时间,并且有可能发生未对准的情况,从而导致产量降低和制造这些晶圆的时间大幅增加,导致多重曝光路线耗时且价格昂贵,还会影响整体良率。 综上,虽然依靠DUV光刻机生产更先进制程的芯片有难度,但各种多重图形化技术仍有望推动国内半导体制造产业朝更先进发展。

2.2 三维异构技术:另辟蹊径规避部分物理瓶颈

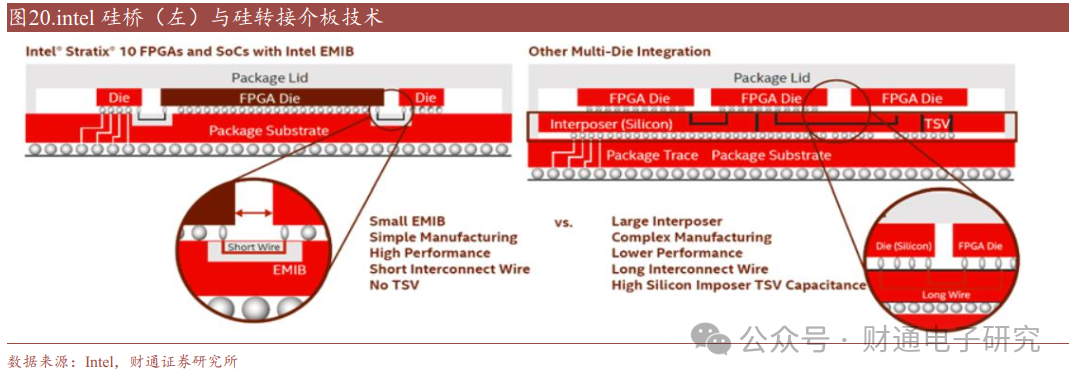

随着各类型芯片中晶体管数量持续增长,基于摩尔定律的集成电路发展路径遭遇瓶颈,已经无法满足对计算力、存力等更高的需求。

我国先进算力芯片的发展主要面临内存墙、功耗墙、先进制程三大困难。内存墙是源于冯·诺依曼结构将计算和存储分开,数据传输带宽限制了算力发挥,导致计算单元空转;功耗墙限制了终端续航能力、便携性、应用场景扩展;先进制程的技术发展接近物理极限导致成本急剧升高,国内先进制程发展也面临海外在晶圆代工、设备、材料、软件方面的限制。

2015-2025年的过渡期期间,需要大量结构、材料创新,才能勉强支撑摩尔定律。2025年后,所有高性能芯片对集成度要求高、对功耗要求低、带宽要求高的产品都会走向异构集成路线。百万级连线、功能完整的单芯片异构集成有望会成为3DIC的理想形态。

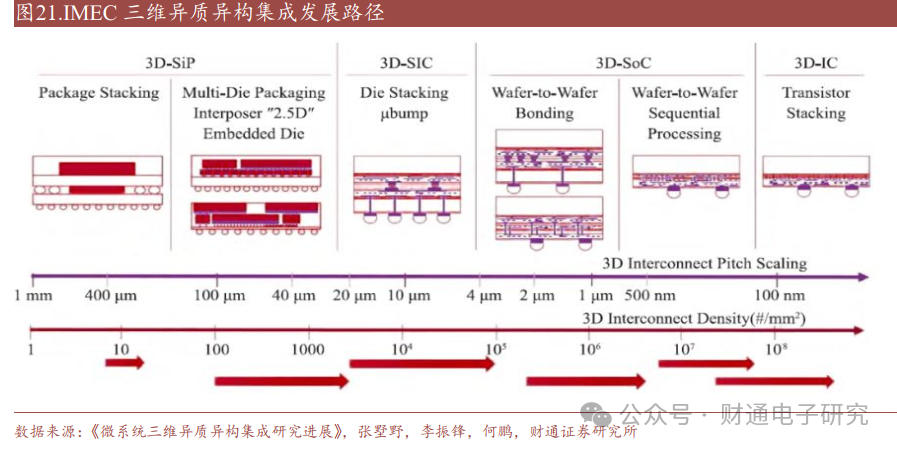

三维异构集成的关键技术包括实现信号传输和互连的硅通孔技术、硅桥技术、玻璃通孔技术、再布线层技术、微凸点技术等,不同关键技术相互融合、共同助力三维异构集成技术的发展。印刷电路板(PCB)级别的集成成本低,但最小特征尺寸只能达到10μm左右,5~8μm的特征尺寸只能在局部实现,集成密度继续提高的难度较大。新兴的三维异质异构集成聚焦于亚微米至10μm特征尺寸级别的互联,成本相对较低。晶圆代工级别的集成可在硅/玻璃转接板上,实现更高互联密度,互联结构的特征尺寸甚至可达纳米级,但其工艺的成本较高,产业化大规模应用难度较大。

3D 异构集成技术涉及垂直堆叠内存和逻辑单元,这种垂直集成缩短了数据路径,提高了能源效率,并允许更高的互连密度,可以绕过一些传统上限制芯片性能的物理限制。

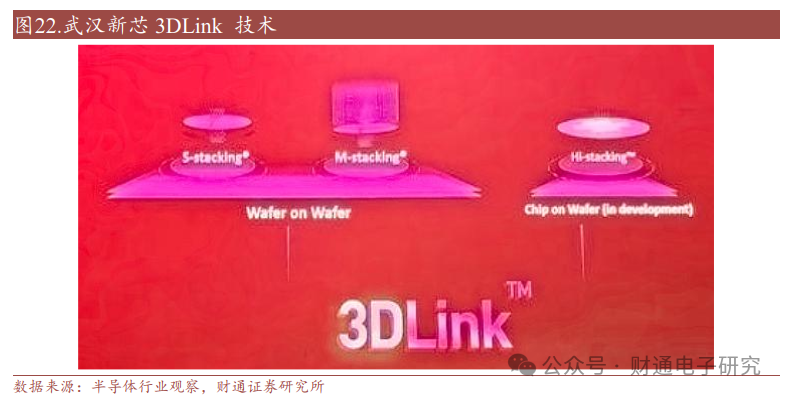

中国大陆的武汉新芯等企业在三维异构集成电路领域有相关研究,有望推动国内三维异构技术加快发展,从而部分缓解先进制程晶圆代工受限的影响。

2.3 新型晶体管结构与材料,有望带来革命性变化

2.3.1 GAA技术助力先进逻辑制程发展

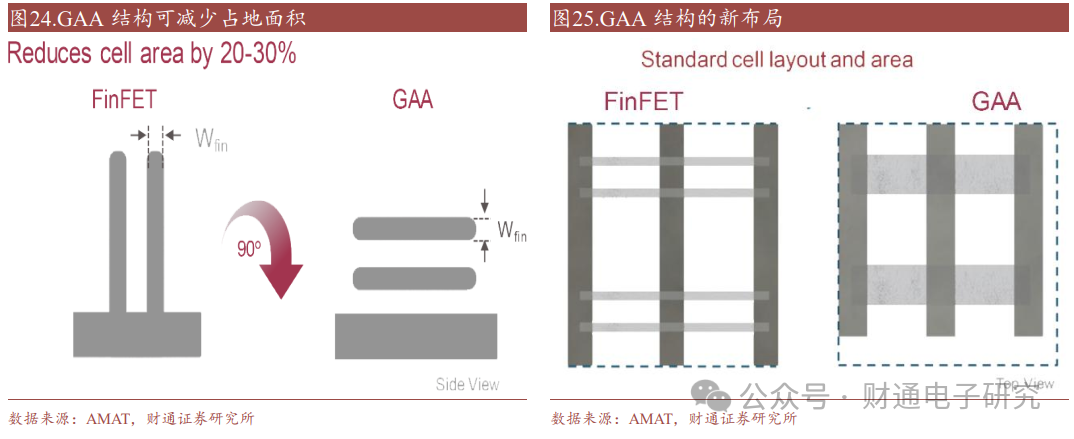

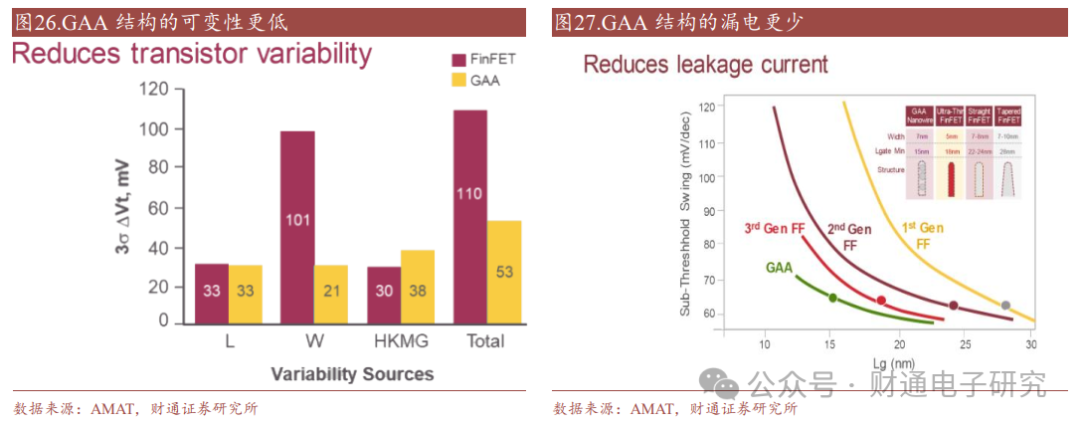

FinFET是鳍场效应晶体管的缩写,是一种先进的晶体管架构,与平面结构(PLANAR)的晶体管相比,可以更好地控制流经沟道的电流。这样可以降低漏电流,从而提高性能和电源效率。但随着 FinFET 的尺寸越来越小,鳍片变得越来越窄、越来越高,FinFET 架构正在被推向极限,业界开始转向被称为全环绕栅极(GAA)的新架构,以进一步提高性能和电源效率。

全环绕栅极(GAA)是一种晶体管架构,将 FinFET的通道设计侧向转动,使通道是水平的而不是垂直的;与FinFET架构中的三面环绕通道不同,GAA结构中的结构为四面环绕通道,可更好地控制晶体管开关。GAA晶体管具有更低的可变性、更高的性能、更低的功耗。

GAA结构集成电路的生产制造过程,借鉴了许多FinFET的成熟工艺。但是也有包括外延、选择性去除、集成材料解决方案、电子束计量在内的新技术。

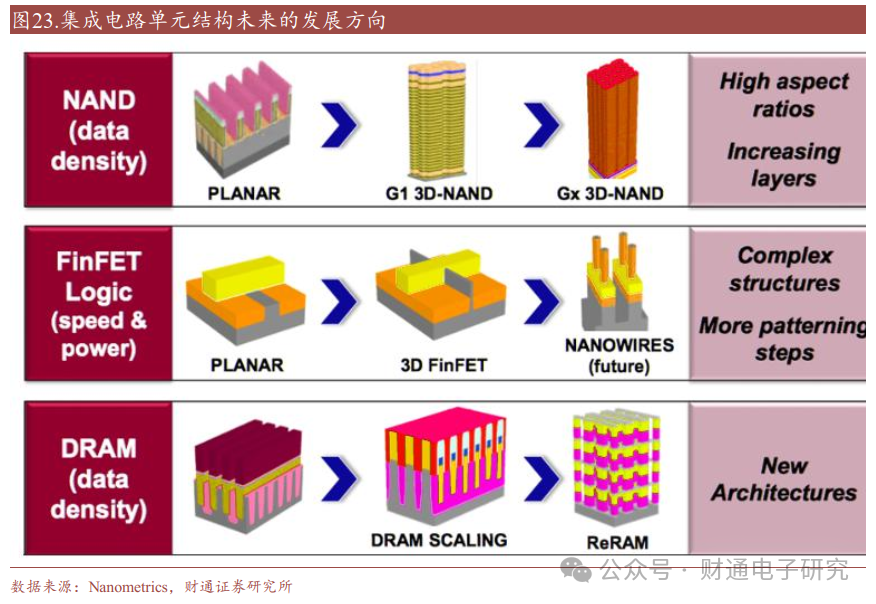

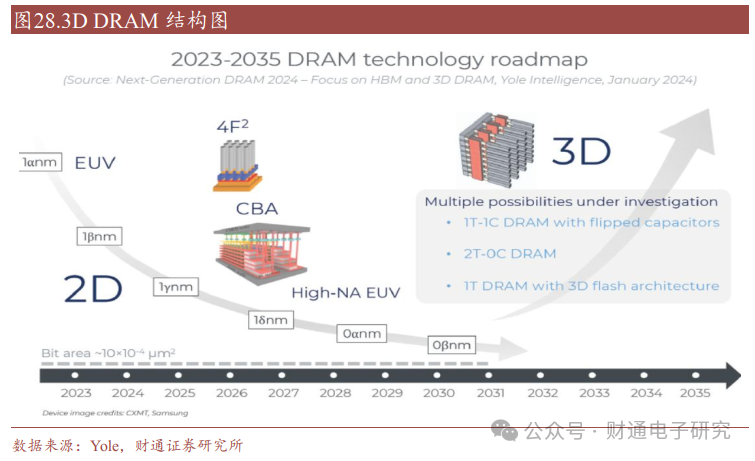

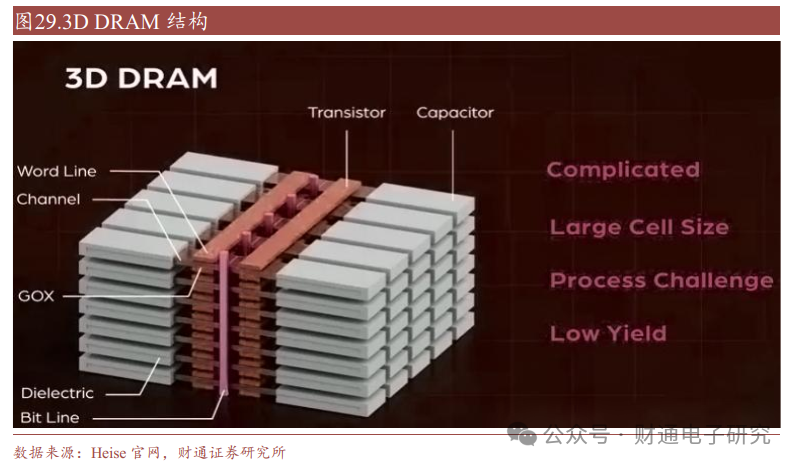

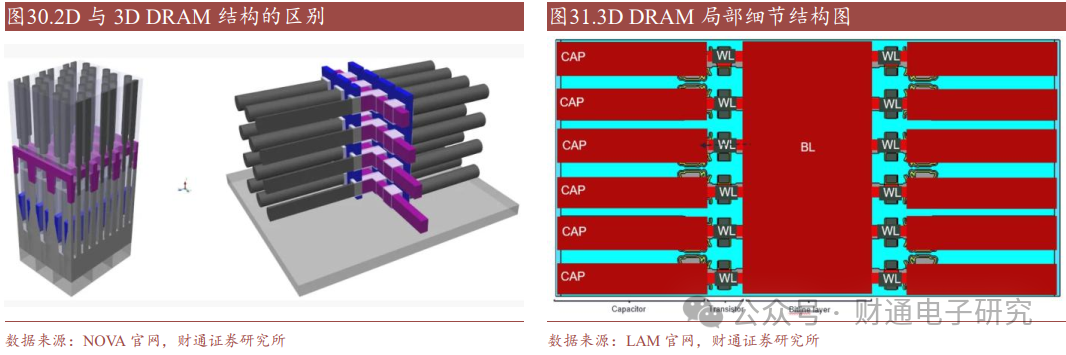

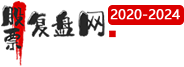

2.3.2 3D DRAM技术助力内存产业突破原有极限

DRAM芯片制程工艺已达到10nm级别,虽然还未达到最后极限,但工艺完整性、成本、电容器漏电和干扰、传感裕度等方面的挑战愈发明显,要在更小的空间内实现稳定的电荷存储和读写操作变得更困难;通过增高电容器并减小面积,以提高电容密度的方法即将面临极限。

云计算、人工智能、大数据分析等领域对高性能DRAM内存芯片的需求持续攀升,在市场需求和技术创新的驱动下,3D DRAM成为了业界迫切想突破DRAM工艺更高极限的新路径。

3D DRAM是一种具有全新结构的存储芯片,它的结构与较为成熟的3D NAND有类似之处,但是制造难度更大。3D DRAM架构并非简单地将2D DRAM组件堆叠在一起,也与HBM不同;3D DRAM的架构经过重新设计,生产过程需要采用先进的刻蚀、沉积、GAA等工艺技术和先进封装技术。

3D DRAM设计重点是解决制程节点微缩和多层堆叠的难题,另外,还有电容器和晶体管微缩,以及单元间连接和通孔阵列,也要制定相应的工艺规格。

美光从2019年起就开始了3D DRAM的研究,拥有30多项与3D DRAM相关的专利,获得的专利数量是三星和SK海力士的2~3倍。三星电子预计,DRAM产业将于2030年前将制程压缩至10nm以下,现有设计方案难以进一步扩展;三星在半导体产业会议Memcon 2024上表示,2025年后将进入3D DRAM时代。

SK 海力士报告其五层堆叠的 3D DRAM 内存良率已达 56.1%,实验中的 3D DRAM 展现出与目前 2D DRAM 相似的特性。但SK海力士也指出3DDRAM 表现出不稳定的性能特征,需要堆叠 32 到 192 层存储单元才能实现普遍应用。国产DRAM芯片制造商长鑫存储(CXMT),在旧金山举行的第69 届IEEE 国际电子元件年会(IEDM)上发表了一篇论文,展示了环绕式闸极结构(GAA)技术,该论文描述了与新型DRAM结构可行性相关的基础研究。

综上3D DRAM技术有望助力国内DRAM内存产业部分缓解光刻机受限带来的困难。

3

3 投资建议:

3.1 晶圆代工:国内晶圆代工需求有望持续增长

晶圆代工是实现半导体产业自主可控的核心阵地,多重图形化、三维异构、新型晶体管技术有望助力国内晶圆代工产业追赶国际领先水平。伴随着国内晶圆代工新产线分批次投入运营,新制程研发稳步推进,中芯国际、华虹公司、中芯集成等晶圆代工企业的营收有望稳步增长,盈利能力也有望不断强化。此外,随着国产设备、零部件、材料的技术水平不断提升,国内晶圆代工企业有望不断改善制造工艺并迈向更先进制程,为国产GPU、手机SOC等高端芯片打下坚实基础。

3.2 半导体设备:半导体供应链上游基石

伴随中国大陆的晶圆代工、先进封装、存储器IDM产线有望持续扩张,并产生大量半导体设备采购需求。北方华创、中微公司、拓荆科技、微导纳米、华海清科、盛美上海、精测电子、中科飞测、至纯科技等半导体设备企业有望深度受益,保障国内供应链自主可控,并实现营收规模的快速扩张。随着海外半导体设备出口管制日趋严格,国产设备的导入验证速度有望大幅度提升。国家层面强调科技创新,光刻机、量检测设备等光学领域有望加快弥补短板。

3.3 半导体材料与零部件企业:半导体供应链的血液

晶圆厂产线的运转,需消耗大量半导体材料与零部件。

鼎龙股份的抛光垫,菲利华的石英材料,安集科技的抛光液,昌红科技的晶圆载具,兴森科技的载板,彤程新材、华懋科技的光刻胶产品,金宏气体、雅克科技、正帆科技的气体,江丰电子的靶材等,可运用于集成电路生产,未来市占率有望不断提升。

珂玛科技的陶瓷零部件产品,国力股份、英杰电气的电容器与射频电源产品,可用于刻蚀或薄膜沉积设备;京仪装备、美埃科技的产品可用于晶圆厂厂务环节;富创精密、新莱应材、江丰电子的机械加工类零部件和阀门等产品,半导体设备与晶圆厂企业均有需求。零部件企业不断推进研发和验证,有望受益于国内半导体产业链的发展与半导体行业景气度回升。

4

6 风险提示

半导体需求不及预期:全球半导体市场复苏仍有不确定性,叠加宏观经济增长放缓、地缘政治风险,可能导致半导体需求整体不及预期,拖累相关公司业绩。

技术研发不及预期:先进半导体技术研发难度较大;芯片设计、制造工艺、设备、零件、材料存在较长的研发和验证周期。若新产品研发验证或客户导入进度慢于预期,可能会对相关公司的业绩造成不利影响。

海外供应链风险:国内半导体供应链部分技术仍依赖海外,若海外限制加剧,可能会对国内半导体供应链企业业绩产生不利影响。

行业竞争加剧:存储器与半导体制造、设备、零部件、材料等领域新进入者不断增多,若未来竞争加剧,可能会对相关企业的业绩产生不利影响。

VIP复盘网

VIP复盘网